# Transparent Dynamic Optimization: The Design and Implementation of Dynamo

Vasanth Bala, Evelyn Duesterwald, Sanjeev Banerjia HP Laboratories Cambridge HPL-1999-78 June, 1999

E-mail: vas@hpl.hp.com

dynamic optimization, compiler, trace selection, binary translation Dynamic optimization refers to the *runtime* optimization of a *native* program binary. This report describes the design and implementation of Dynamo, a prototype dynamic optimizer that is capable of optimizing a native program binary at runtime. Dynamo is a realistic implementation, not a simulation, that is written entirely in user-level software, and runs on a PA-RISC machine under the HPUX operating system. Dynamo does not depend on any special programming language, compiler, operating system or hardware support.

Contrary to intuition, we demonstrate that it is possible to use a piece of software to improve the performance of a native, statically optimized program binary, while it is executing. Dynamo not only speeds up real application programs, its performance improvement is often quite significant. For example, the performance of many +O2 optimized SPECint95 binaries running under Dynamo is comparable to the performance of their +O4 optimized version running without Dynamo.

## Contents

| 1 | INTRODUCTION                                     | 7  |

|---|--------------------------------------------------|----|

| 2 | RELATED WORK                                     | 9  |

| 3 | OVERVIEW                                         | 11 |

|   | 3.1 Design Goals                                 | 11 |

|   | 3.2 How Dynamo works                             |    |

|   | 3.3 Innovative features                          |    |

|   | 3.4 Bailing out to direct execution              | 14 |

|   | 3.5 System calls                                 | 14 |

|   | 3.6 Self-modifying code                          | 15 |

| 4 | MEMORY LAYOUT                                    | 16 |

|   | 4.1 Address space separation                     | 18 |

| 5 | CONTROL                                          | 20 |

| _ | 5.1 Context switches                             |    |

|   | 5.2 Trapping control                             |    |

|   | 5.3 Signal handling                              |    |

| 6 | INTERPRETER                                      | 24 |

|   | 6.1 Plug-in interpreter interface                | 24 |

|   | 6.2 Interpretation via just-in-time translation  | 25 |

| 7 | TRACE SELECTOR                                   | 27 |

|   | 7.1 Online profiling                             | 27 |

|   | 7.2 Speculative trace selection (SPECL)          | 28 |

|   | 7.2.1 Basic block selection (BLOCK)              | 29 |

|   | 7.2.2 Static trace selection (STATIC)            |    |

|   | 7.2.3 Two-level hierarchical selection (2-LEVEL) |    |

|   | 7.3 Trace selection rate                         |    |

|   | 7.4 Bailing out                                  |    |

|   | 7.5 Evaluation                                   |    |

|   | 7.6 Trace quality metric                         |    |

|   | 7.7 Selection threshold                          | 38 |

| 8 | FRAGMENT OPTIMIZER                               | 40 |

|   | 8.1 Dynamic optimization opportunities           | 41 |

|   | 8.1.1 Exposed partial redundancies               |    |

|   | 8.1.2 Suboptimal register allocation             |    |

|   | 8.1.3 Shared library invocation                  |    |

|   | 8.2 Intermediate form                            |    |

|   | 8.3 Fragment formation                           |    |

|   | 8.3.1 Direct branch Adjustments                  | 46 |

|     | 8.3.2    | Indirect branch Adjustments               |    |

|-----|----------|-------------------------------------------|----|

|     | 8.3.3    | Linker Stubs                              |    |

|     |          | mization                                  |    |

|     | 8.4.1    | Optimization levels                       |    |

|     | 8.4.2    | Speculative optimizations                 |    |

|     | 8.4.3    | Multi-versioning optimization             | 49 |

|     | 8.4.4    | Fragment-link-time optimization           | 49 |

|     | 8.5 Und  | esirable side-effects of optimization     | 51 |

|     | 8.6 Reg  | 52                                        |    |

|     |          | erimental evaluation                      |    |

| 9   | ED A C   | SMENT LINKER                              | EC |

| 9   |          |                                           |    |

|     |          | tting the fragment code                   |    |

|     |          | and cons of branch linking                |    |

|     |          | records and the fragment lookup table     |    |

|     |          | et branch linking                         |    |

|     |          | rect branch linking                       |    |

|     |          | ter stubs revisited                       |    |

|     |          | nch unlinking                             |    |

|     | 9.8 Pert | ormance benefit from linking              | 62 |

| 10  | FRAC     | SMENT CACHE MANAGER                       | 63 |

| . • |          | ragment Cache design                      |    |

|     |          | Vorking-set based Fragment Cache flushing |    |

|     | 10.2.1   | The case for Fragment Cache flushing      |    |

|     | 10.2.2   | Selecting a time to flush                 |    |

|     | 10.2.3   | Performance: memory usage                 |    |

|     | 10.2.4   | Performance: speedups                     |    |

|     |          | Iternative placement strategy             |    |

|     | 10.3.1   | Functionality and behavior                |    |

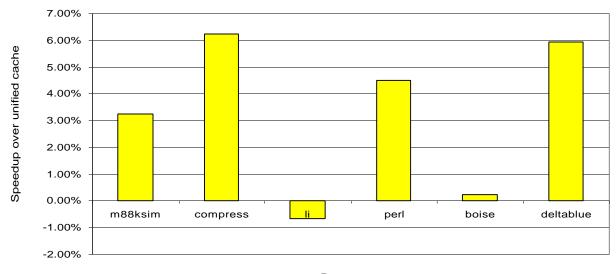

|     | 10.3.1   | Performance Performance                   |    |

|     | 10.3.2   | r errormance                              | 13 |

| 11  | SIGN     | AL HANDLER                                | 78 |

|     |          |                                           |    |

| 12  |          | FORMANCE SUMMARY                          |    |

|     |          | xperimental framework                     |    |

|     |          | xperimental results                       |    |

|     |          | ynamo code and memory footprint           |    |

|     |          | ynamo on highly optimized programs        |    |

|     |          | Tachine specific performance: the PA-8000 |    |

|     | 12.5.1   | Branch prediction                         |    |

|     | 12.5.2   | Indirect branches                         | 85 |

|     | 12.5.3   | Virtual memory                            | 85 |

|     | 12.6 O   | ther programs and processors              | 85 |

|     | 12.6.1   | Program traits                            | 86 |

|     | 12.6.2   | Machine traits                            | 87 |

|     |          |                                           |    |

| 12  | CVCT     | EM DEVELOPMENT TOOLS AND LITH ITIES       | 90 |

|    | 13.1 Th | e system profiler - sprof                          | 89 |

|----|---------|----------------------------------------------------|----|

|    | 13.1.1  | Specifying what to profile: the profiling registry | 89 |

|    | 13.1.2  | Gathering profiling data: timer interrupts         |    |

|    | 13.1.3  | Reporting profiling data: the back-end             | 90 |

|    | 13.1.4  | Examples of profiling data                         | 91 |

|    | 13.2 Me | emory allocators                                   | 93 |

|    | 13.2.1  | The mempool allocator                              | 93 |

|    | 13.2.2  | The poolmalloc allocator                           | 94 |

|    | 13.2.3  | Memory usage in Dynamo                             |    |

|    | 13.2.4  | Retrospective                                      |    |

| 14 | CONC    | CLUSION                                            | 96 |

| 15 | ACKN    | OWLEDGEMENTS                                       | 98 |

| 16 | REFE    | RENCES                                             | 99 |

## Figures

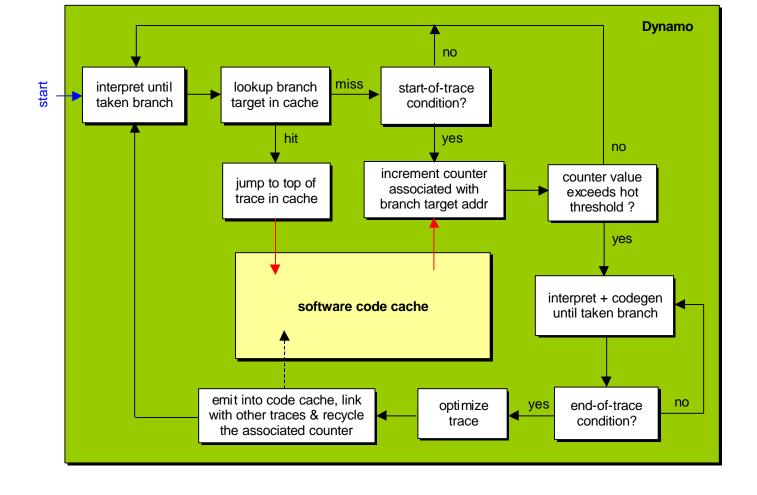

| Figure 1: How Dynamo works                                                                           | 12 |

|------------------------------------------------------------------------------------------------------|----|

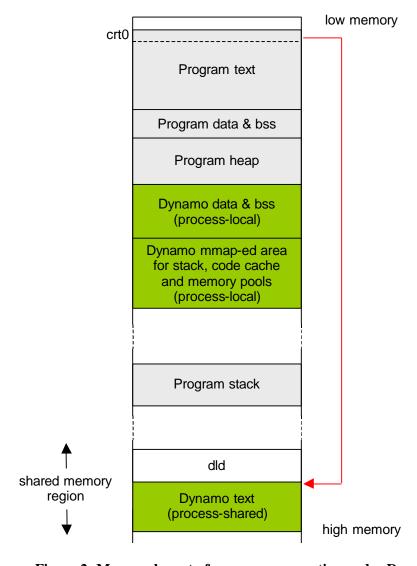

| Figure 2: Memory layout of a program executing under Dynamo                                          | 17 |

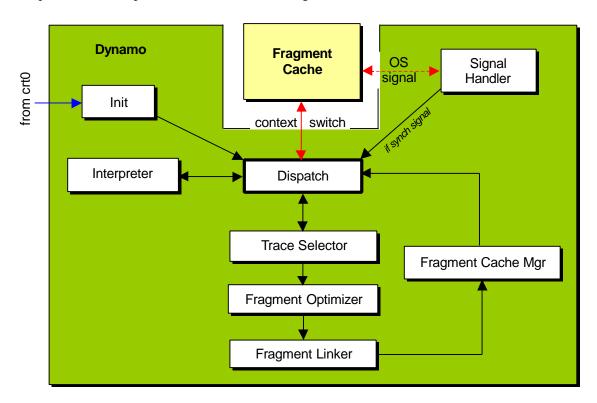

| Figure 3: Control flow between the components of the Dynamo system                                   |    |

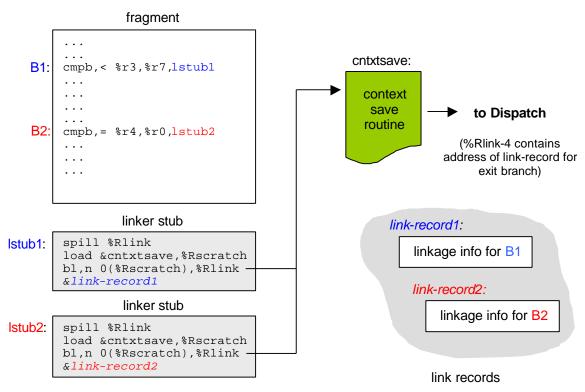

| Figure 4: Use of linker stubs to trap control on a Fragment Cache exit                               |    |

| Figure 5: Handshake between the Interpreter and Trace Selector                                       |    |

| Figure 6: Interpretive overheads                                                                     |    |

| Figure 7: Dynamo's trace selection scheme with trace heads shown in bold                             |    |

| Figure 8: 2-Level hierarchical selection (2-LEVEL)                                                   |    |

| Figure 9: Average trace selection rate                                                               |    |

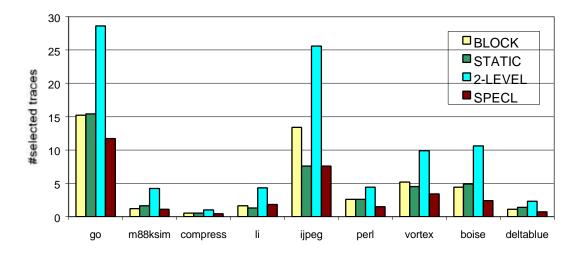

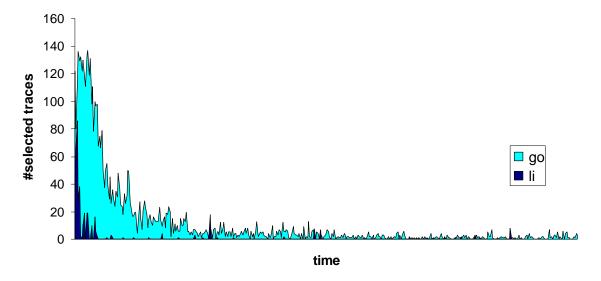

| Figure 10: Trace selection rate for go and li                                                        |    |

|                                                                                                      |    |

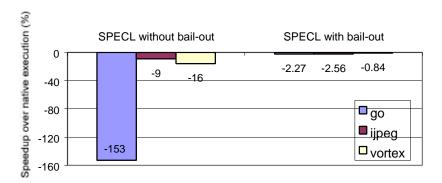

| Figure 11: Overall Dynamo speedup based on SPECL trace selection without and with bail-ou            |    |

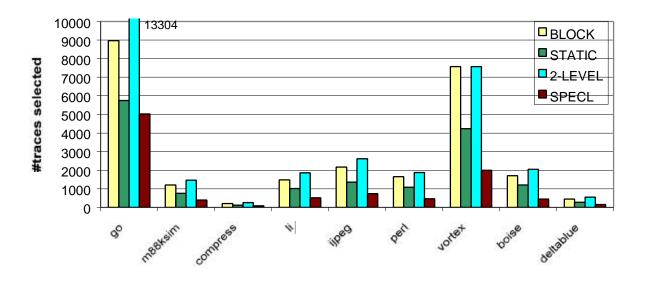

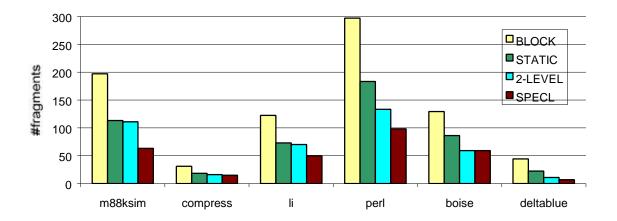

| Figure 12: Number of traces selected by each selection scheme                                        |    |

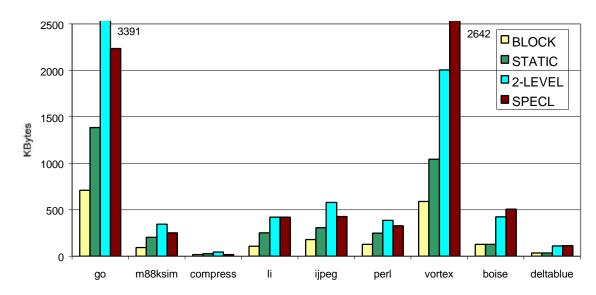

| Figure 13: Accumulated fragment size in Kbytes for each selection scheme                             |    |

| Figure 14: 90%-Cover sets                                                                            |    |

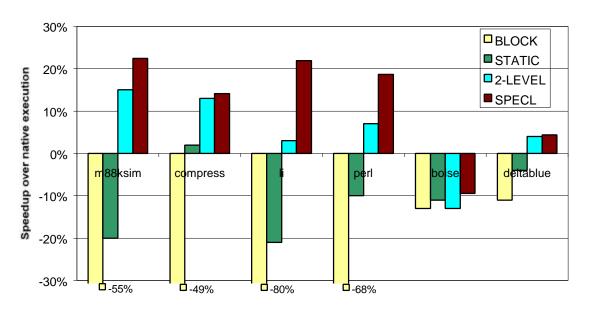

| Figure 15: Overall Dynamo speedup with varying selection schemes                                     |    |

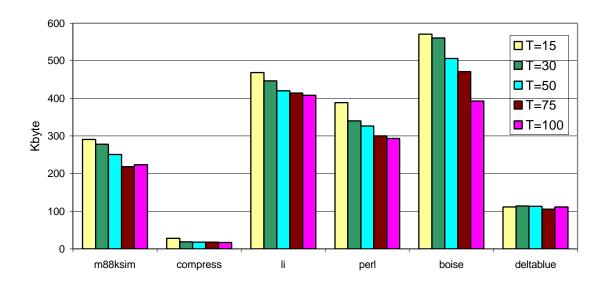

| Figure 16: Accumulated fragment size with varying threshold T                                        |    |

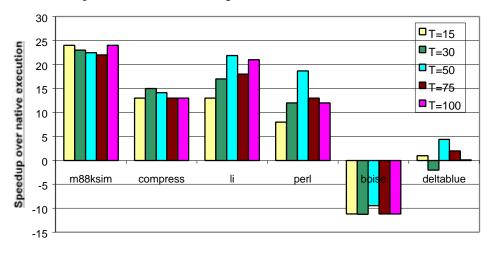

| Figure 17: Overall Dynamo speedup with varying trace selection threshold for SPECL                   |    |

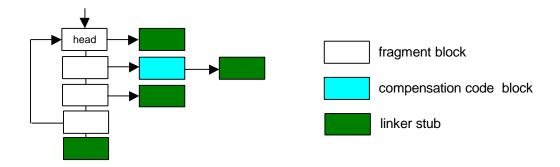

| Figure 18: Anatomy of a fragment                                                                     |    |

| Figure 19: (i) Indirect branch with actual target 0x20, and (ii) its conversion into a direct branch | h  |

|                                                                                                      | 46 |

| Figure 20: Example of guarded load optimization                                                      | 49 |

| Figure 21: Example of link-time optimization                                                         | 50 |

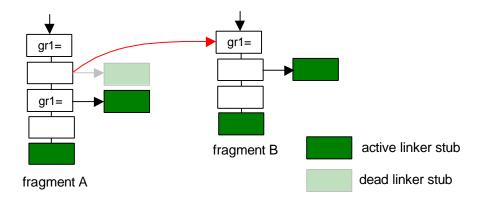

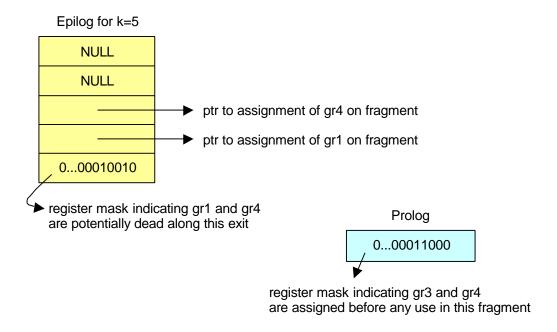

| Figure 22: Fragment epilog and prolog used for link-time optimization                                |    |

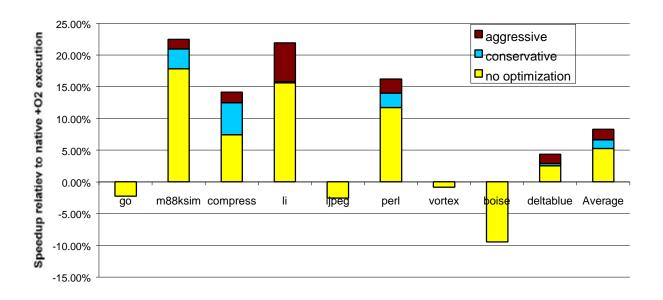

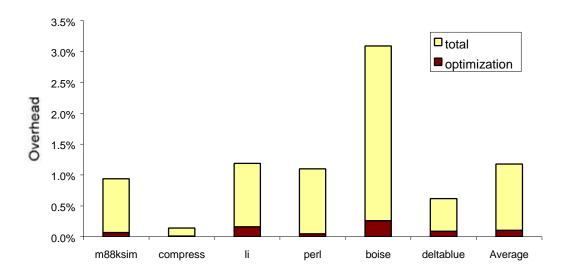

| Figure 23: Overall Dynamo speedup with optimization contribution                                     |    |

| Figure 24: Optimization overhead                                                                     |    |

| Figure 25: The linker stub template                                                                  |    |

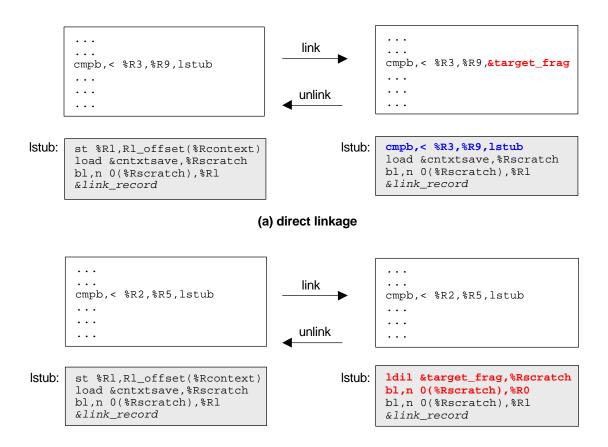

| Figure 26: Illustration of linking and unlinking                                                     |    |

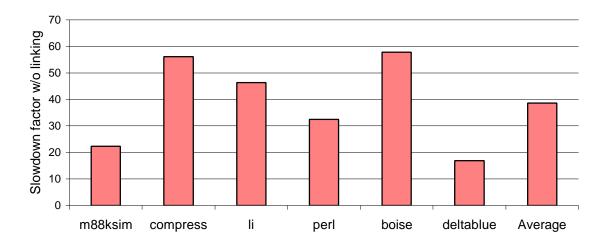

| Figure 27: Performance slowdown when linking is disabled                                             |    |

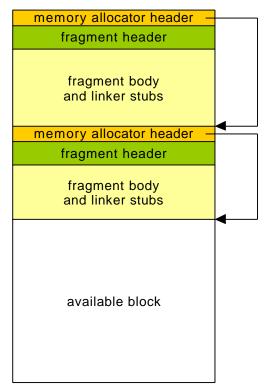

| Figure 28: Fragment Cache memory map with 2 fragments                                                |    |

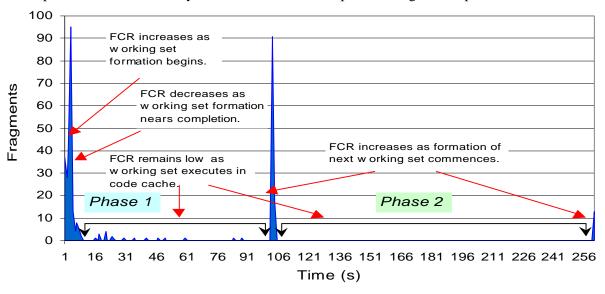

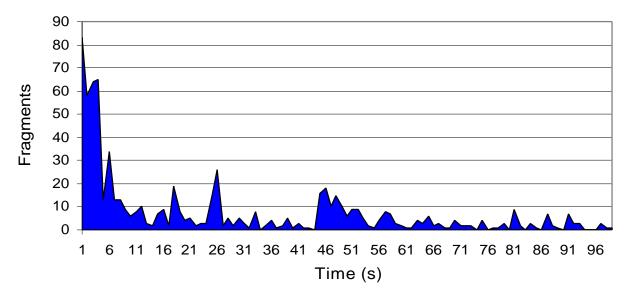

| Figure 29: Fragment creation rate pattern for m88ksim                                                |    |

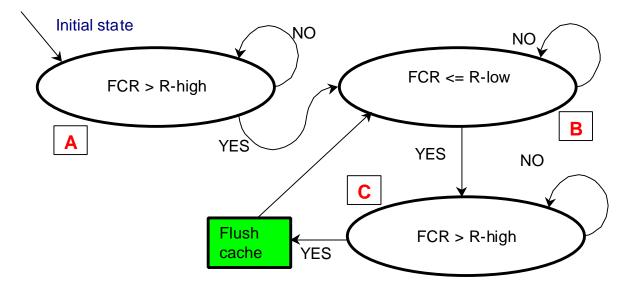

| Figure 30: State diagram for phase change detection logic                                            |    |

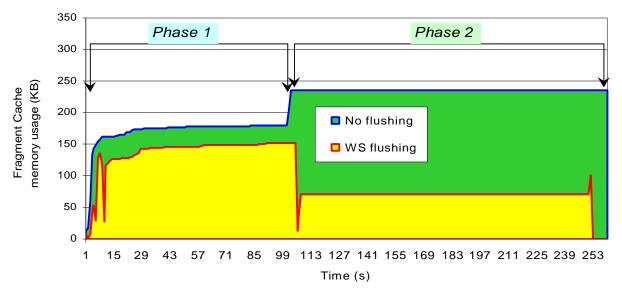

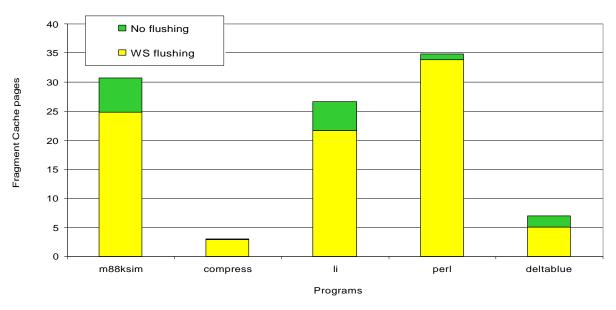

| Figure 31: Fragment Cache memory usage with and without WS flushing                                  |    |

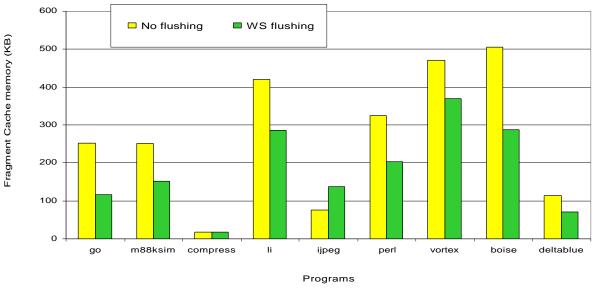

|                                                                                                      |    |

| Figure 32: Dynamic changes in Fragment Cache memory usage with WS flushing in m88ksim                |    |

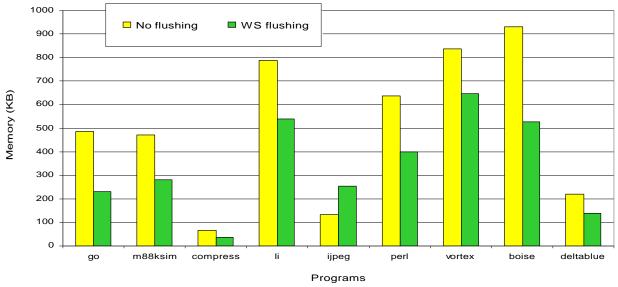

| Figure 33: Memory usage in dynamic pools with and without WS flushing                                |    |

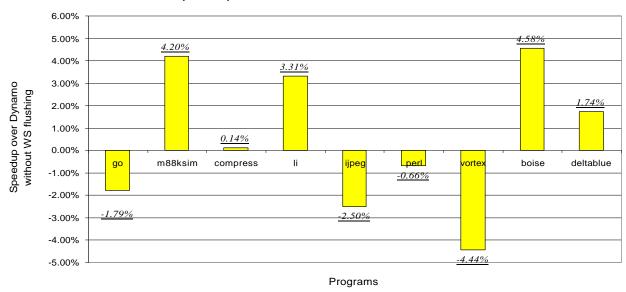

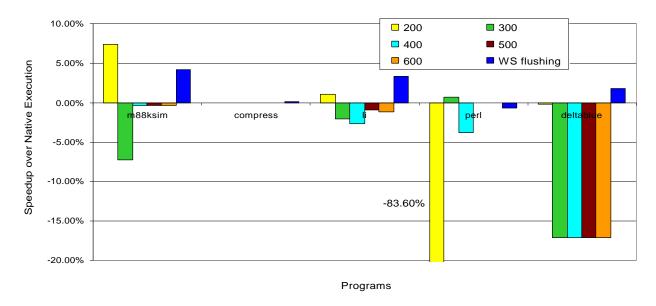

| Figure 34: Run time performance of WS flushing compared to no WS flushing                            |    |

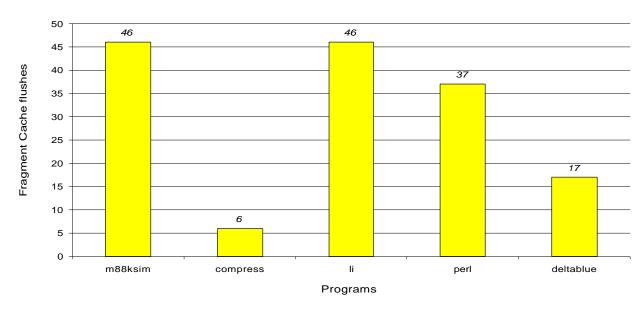

| Figure 35: Number of flushes caused by WS flushing                                                   |    |

| Figure 36: Run time performance of interval flushing versus WS flushing                              |    |

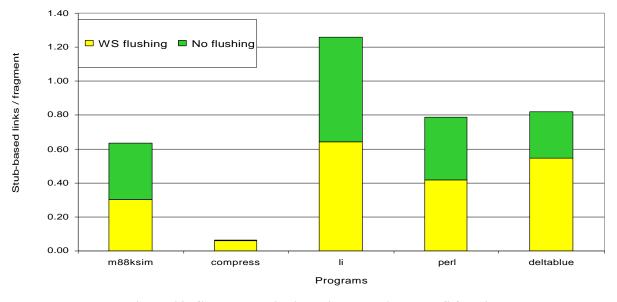

| Figure 37: Fragment Cache page usage with and without WS flushing                                    |    |

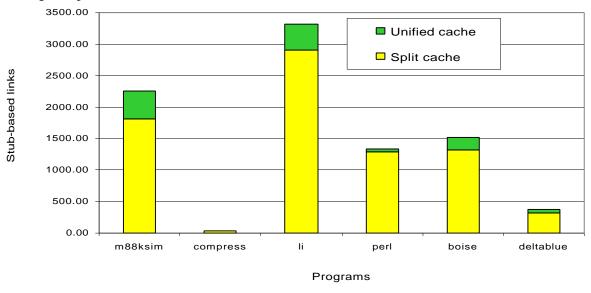

| Figure 38: Stub-based linking with and without WS flushing                                           |    |

| Figure 39: Run time performance of the split cache                                                   |    |

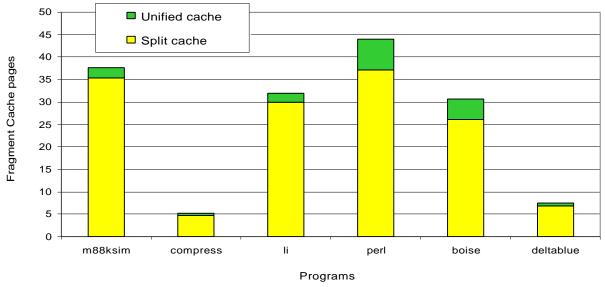

| Figure 40: Fragment Cache page usage with and without the split cache                                | 76 |

| Figure 41: Stub-based linking with and without the split cache.                                      | 77 |

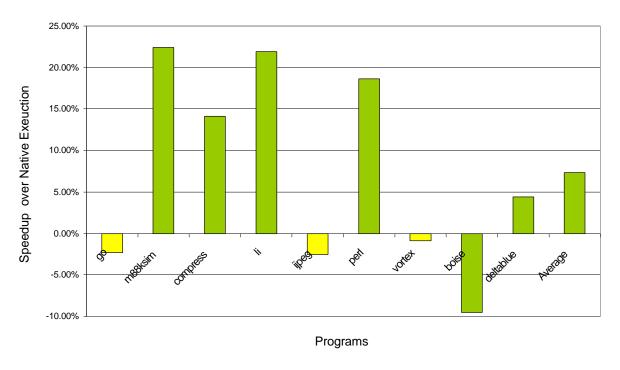

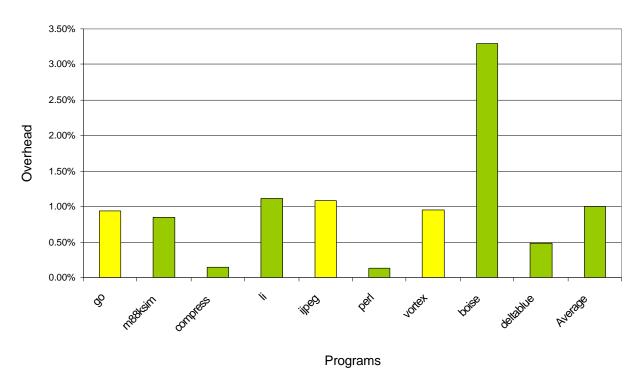

| Figure 42: Dynamo performance (light/yellow bars indicate that Dynamo bailed-out)                    | 81 |

| Figure 43: Dynamo overhead (light/yellow bars indicate that Dynamo bailed-out)                       |    |

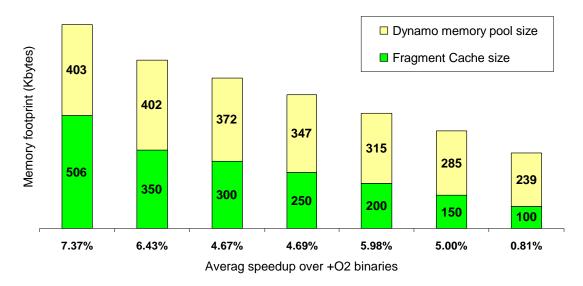

| Figure 44: Fragment Cache and Dynamo memory pool footprint                                           |    |

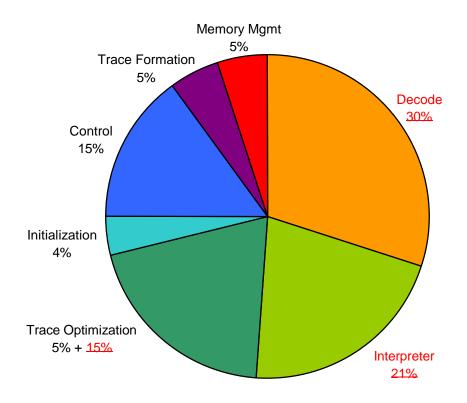

| Figure 45: Breakdown of the Dynamo code footprint ( <u>underline</u> indicates PA-dependent code)    |    |

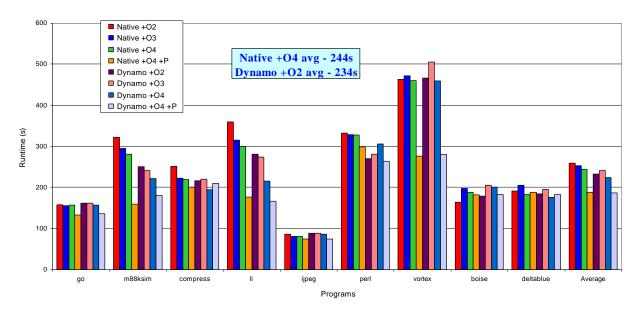

| Figure 46: Performance comparison of Dynamo against native execution                                 |    |

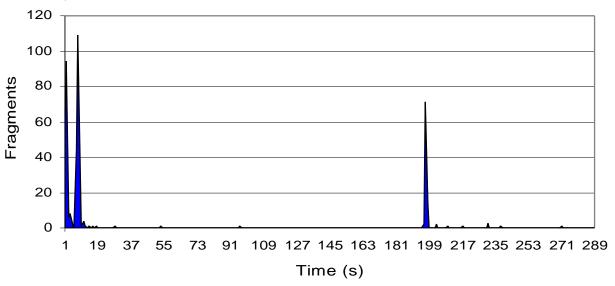

| Figure 47: Fragment creation rate pattern for perl                                                   |    |

|                                                                                                      |    |

| Figure 48: Fragment creation rate pattern for ijpeg                 | 87 |

|---------------------------------------------------------------------|----|

| Figure 49: Fragment Cache hit rate and breakdown of Dynamo overhead |    |

| Figure 50: Counter values from registered functions                 | 92 |

| Figure 51: Fragment profiling data                                  | 92 |

## 1 Introduction

As software and hardware technologies evolve in a rapidly changing marketplace, there are several forces pulling in opposite directions, making cost-effective performance delivery ever more challenging.

Consider the high-end server market for example. In the drive for greater performance, microprocessors now provide capabilities for compiler software to take on a greater role in performance delivery [Gwennap 1997]. In the meantime, however, trends in software technology are gradually increasing the obstacles to static compiler optimization. The widespread use of object-oriented programming languages and the trend towards shipping software binaries as collections of DLLs (dynamically linked libraries) rather than monolithic binaries, has resulted in a greater degree of run-time binding. Run-time binding offers the advantage of being able to ship software patches to the customer after the product sale has been made, and also eases the integration of third-party middleware into the product. Unfortunately, it also makes traditional compiler optimization, which operates on the statically bound scope of the program, more difficult. From a practical standpoint, the use of compiler optimization is also limited by the inability to effectively debug highly optimized code. For this reason, many ISVs (independent software vendors) are reluctant to ship software binaries that are compiled with high levels of optimization, in spite of their improved performance potential.

In the desktop PC market on the other hand, performance delivery is complicated by the prevalence of legacy binaries. Recompilation is clearly an impractical means for improving program performance, given the sheer volume of legacy software. As a result, the microprocessor hardware has taken on most of the performance burden. Unfortunately, when system prices drop rapidly but performance expectations don't, this strategy starts to become impractical.

Then there is the emerging Internet and mobile communications marketplace. In a networked device where code can be downloaded and linked in on the fly, the role of traditional performance delivery mechanisms like static compiler optimization is unclear. Furthermore, the tendency of advanced compiler optimizations to produce fat program binaries restricts their applicability in small memory-footprint mobile devices.

With all of these forces pulling in opposite directions, there is a need for new performance delivery technologies to bridge the widening gap. It is clear that the current model, where the performance delivery task is divided only between the microprocessor hardware and the compiler software is very limited for use in the newly emerging computing environment.

In this report we propose a radically different performance delivery technology. The application is optimized at the time the native bits are *executed* on the microprocessor, rather than when the native bits are *created* as in the case of a static compiler. We refer to this as *dynamic optimization*, and in principle, it is similar to what a superscalar reorder buffer does in a modern microprocessor: the *runtime optimization* of a *native* instruction stream. In contrast to a hardware dynamic optimizer however, our scheme works entirely in software, and yet retains the "transparent" nature of hardware dynamic optimization. One can view this as a "virtual microprocessor", where the dynamic optimization component is implemented in software while the CPU core is implemented in hardware.

We have implemented a prototype called **Dynamo** that demonstrates the feasibility of this idea in a very compelling way, and represents the culmination of three years of research conducted at Hewlett-Packard Labs [Bala and Freudenberger 1996]. Dynamo is a transparent dynamic optimizer that performs optimizations at runtime on a native binary. Dynamo does not rely on any annotations in the original program binary. It uses interpretation as a means of observing program behavior without having to instrument it. This allows Dynamo to operate on legacy binaries without recompilation or instrumentation. No information is written out during or after the program's execution for consultation during a later run, and no pre-runtime analysis is

done on the binary. Instead, the profiling information that is collected via interpretation is consumed on the fly to dynamically select hot instruction traces from the program. The hot traces are optimized using a low overhead optimizer and placed in a software code cache. Subsequent occurrences of these traces cause the cached version to be executed, giving a performance boost. The original loaded image of the program binary is never modified by Dynamo, allowing Dynamo to even run programs that modify their own text image. The operation of Dynamo is thus completely transparent to the end-user.

The Dynamo system is implemented entirely in software, and does not depend on any special compiler, operating system or hardware support. Dynamo has a compact code footprint, allowing it to comfortably fit within typical ROM constraints if necessary, and its data memory footprint is configurable for a variety of performance/memory tradeoffs. This allows the dynamic optimization technology to be deployed in a wide range of platforms, from large servers to embedded devices.

Dynamo is a fundamentally different performance delivery vehicle. Unlike a traditional compiler, the ISV is not responsible for enabling the optimization. In contrast to a JIT, there is no translation component: the input is a native instruction stream. And unlike a superscalar microprocessor, no special hardware is used for doing the optimization. Dynamo is a realistic implementation, and not a simulation. Our prototype currently runs on a PA-8000 workstation under the HPUX 10.20 (HP Unix) operating system.

## 2 Related Work

A lot of work has been done on dynamic translation as a technique for non-native system emulation [Bedichek 1995; Cmelik and Keppel 1993; Herold 1998; Hohensee et al. 1996; Insignia 1991; May 1987; Stears 1994, Witchel and Rosenblum 1996]. The basic idea is simple: interpretation is too expensive a way to emulate a long running program on a host machine. Caching the native code translations of frequently interpreted regions can lower the overhead. If sufficient time is spent executing the cached translations to offset the overhead of interpretation and translation, the caching strategy will generally outperform interpretation in performance. Some implementations even bypass the interpreter completely and translate to native code prior to executing every unit [Cramer et al. 1997; Griswold 1998; Ebcioglu and Altman 1997]. More recently, hybrid dynamic translation systems are emerging that use a combination of software and custom hardware [Kelly et al. 1998].

Dynamic *optimization* is different from dynamic translation: the input is a *native* program binary, so there is no "translation" step involved. While the goal of a dynamic translator is to beat the performance of pure interpretation, the goal of a dynamic optimizer is to beat the performance of the input program executing directly on the host machine.

Dynamic optimization is also different from dynamic *compilation* as generally defined in the literature. In dynamic compilation, the programmer either explicitly requests that a specific part of the program be compiled at runtime via program annotations [Auslander et al. 1996; Leone and Dybvig 1997 <sup>1</sup>; Consel and Noel 1996; Leone and Lee 1996] or uses a language that allows efficient runtime compilation [Engler 1996; Holzle 1994; Poletta et al. 1997]. The code generated at compile-time contains stubs to transfer control at runtime to a compiler, which then dynamically generates the native executable code. In contrast, we view dynamic *optimization* as a much more transparent process. No special programming language or compiler annotations should be necessary to trigger its activation. It should work on already compiled native code without the need for any additional processing, including instrumentation of the binary. In the case of dynamic compilation, the runtime compiler is a necessary step for the execution of the program, whereas in the case of dynamic optimization, it is not. At any moment, the dynamic optimizer has the option of "bailing out" and letting the input program execute directly on the underlying processor.

There are several implementations of *offline binary translators* that also perform native code optimization [Chernoff et al. 1998; Hookway and Herdeg 1997; Sites et al.]. These generate profile data during the initial run via emulation, and perform background translation together with optimization of hot spots based on the profile data. Again, this strategy is not transparent in the sense that the dynamic optimizer is. The benefit of the optimization is only available during subsequent runs of the program. In the case of a dynamic optimizer, on the other hand, profile data is generated and consumed in the very same run, and no data is written out for use offline or during a later run.

Hardware implementations of dynamic optimizers are now commonplace in modern microprocessors [Kumar 1996; Song et al. 1995; Papworth 1996; Keller 1996]. The optimization unit is a fixed size instruction window, with the optimization logic operating on the critical execution path. The Trace Cache is another hardware alternative that can be extended to do superscalar-like optimization off the critical path [Peleg and Weiser 1994; Rotenberg et al. 1996; Friendly et al. 1998]. But we are unaware of any attempts to implement a transparent dynamic optimizer entirely in software. This is perhaps not without good reason: conventional wisdom

\_

<sup>&</sup>lt;sup>1</sup> The Indiana project is also called "Dynamo". We regret the name collision. When our project was started in the winter of 1995, we were unaware of the other Dynamo project. We have since used the Dynamo name in numerous internal documents, memos, presentations and patent filings, making the task of renaming our project at this stage somewhat more difficult than one might imagine.

flies in the face of the suggestion that a software dynamic optimizer can improve the performance of a compiled native program binary while it executes on the host machine.

## 3 Overview

Dynamic optimization is not intended to replace static compiler optimization, rather the two are for the most part complementary. The static compiler optimizer performs its optimizations based on the static scope of the program, whereas the dynamic optimizer performs its optimizations based on the dynamic scope of the program, after all runtime objects have been bound. The dynamic optimizer can be viewed as performing a last minute correction of the most frequently executed instruction sequences in the running program. This allows it to perform optimizations across dynamically linked procedure call boundaries and virtual function calls, which would be difficult to do in a static compiler. It can also perform runtime path-specific optimizations without having to do extensive code duplication to separate out the path from the surrounding control flow. Dynamic optimization opportunities exist even in programs compiled at the highest static optimization levels.

## 3.1 Design Goals

The vision of a totally transparent software dynamic optimizer is nevertheless a particularly challenging one, given that it has to beat the performance of compiled native code handily in order to gain wide acceptance. The following were the principal design goals for the Dynamo project:

- 1. *Performance*: a program binary under dynamic optimization should run at least as fast as the same program binary running directly on the underlying processor. Input program binaries will be created using the native compiler using the default optimization level (-O). Performance comparison will be based on actual wall-clock time on a real machine, and not simulated cycles.

- 2. *Transparency*: the behavior of the program under dynamic optimization should be indistinguishable from that of the same program running by itself, except for any performance differential. This means guaranteeing reproducibility of behavior even in the presence of signals. It also means preserving any bugs in the original code. A consequence of this is that the original program binary must be loaded at the identical address in memory, and its loaded binary image cannot be modified by the dynamic optimizer.

- 3. *Compactness*: the system should have a compact footprint (no more than a few hundred KB), and its data memory usage should be tunable for different performance/memory tradeoff points. This would allow the system to be deployed in devices ranging from large servers to small handheld mobile gadgets.

- 4. *Instrumentability*: since this is intended to be a research infrastructure, the system should be thoroughly instrumented to study and understand its behavior. Performance should not be impacted when the instrumentation is shut off.

From the outset it was clear that every component of Dynamo would have to be very carefully engineered, because overhead of dynamic optimization is such a critical issue. In that sense, we couldn't afford to merely build a proof-of-concept research prototype; the system had to be fairly robust in order to come even close to meeting the above design goals. Even so, these are difficult goals to achieve, especially since our implementation does not rely on any operating system or hardware support. The transparency goal was by far the most difficult one to meet. While we cannot claim that we have met every aspect of these goals in our prototype, we have managed to come a lot closer than we had imagined would be possible at the start.

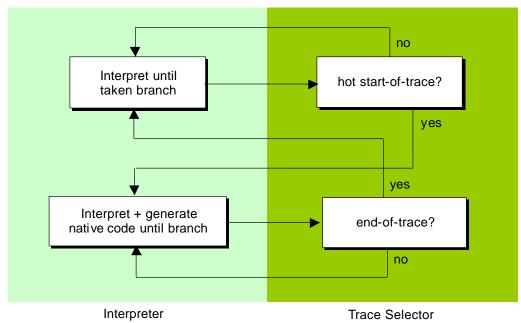

Figure 1: How Dynamo works

## 3.2 How Dynamo works

Dynamo is currently implemented for the PA-RISC platform (a PA-8000 based workstation running HPUX 10.20). It is written in a combination of C and assembler. Although the implementation takes advantage of some features of the PA instruction set architecture to improve the efficiency of certain functions, it does not rely on them for operation. Thus in principle, Dynamo can be ported to other processor architectures.

Figure 1 shows a high level outline of how Dynamo works. Dynamo starts out by interpreting the input program's instructions. The input program must be a user-mode native executable (supervisor-mode programs can create complications that our current prototype cannot yet handle reliably). It can be a legacy binary, and may invoke dynamically linked libraries (shared libraries) and system calls. It can also arm signal handlers. The "interpreter" here is a native instruction interpreter, implemented in software. Interpretation is primarily used as a means for observing program behavior without having to instrument the program binary. As a side effect of interpretation, Dynamo increments counters associated with certain program addresses that satisfy a "start-of-trace" condition (such as the interpretation of a backward taken branch). If a counter value exceeds a preset hot threshold, the interpreter toggles state and goes into "code generation" mode. When interpreting in this mode, the native instructions comprising the trace are emitted into a buffer. When an "end-of-trace" condition is reached, the contents of

this buffer are optimized by a fast, lightweight optimizer. The optimizer makes the trace instructions into an executable unit called a *fragment*, optimizes the fragment, and then hands it to a linker. The linker emits the fragment code into a software code cache, and links it to other fragments already in the cache. The fragment is tagged with the program address corresponding to the first instruction in the sequence (referred to as the "fragment entry point").

Every time the interpreter, when interpreting in its normal mode, interprets a taken branch instruction, it looks up the software cache to see if a fragment exists whose tag is equal to the branch target PC. If there is a hit, control immediately jumps to the top of the fragment, causing that fragment code (and others that may be linked to it) to execute directly on the underlying processor. At this point, the execution of Dynamo is effectively suspended, and the optimized program instructions in the software code cache are executing directly on the processor. The optimized fragments from the software cache gradually start populating the underlying processor's instruction cache, and the end-user perceives a performance boost.

Eventually, a branch exits the software code cache address space, causing control to trap to Dynamo. The execution of the optimized program instructions within the software code cache is now suspended, and Dynamo code is now executing on the underlying processor. A counter associated with the exit branch target is incremented, and if this counter exceeds another preset threshold, the interpreter is invoked in its code generation mode, causing it to produce a fresh trace. Otherwise, the interpreter is invoked in its normal mode of operation, completing the Dynamo execution loop. The rationale here is that if an exit from a hot trace itself gets hot, a new trace should be formed starting at the exit branch target. Gradually, as more and more hot traces are materialized in the software code cache, an increasingly greater time is spent executing within the software cache, and a correspondingly smaller proportion of time is spent in Dynamo.

### 3.3 Innovative features

At the abstract level of the above description, the working of Dynamo is not very different from that of recent dynamic translator implementations like Shade [Cmelik and Keppel 1994]. Yet, Dynamo's performance is quite startling in comparison to past dynamic translator implementations, especially given that it significantly speeds up *native*, *statically optimized* program binaries. And it manages to do so with a very compact code and data memory footprint (approximately 250 KB and 300 KB respectively in our current version). Three innovations make all of this possible.

The first, and probably the most important, is Dynamo's hot trace selection scheme. It is highly speculative in nature, and uses very minimal profiling. The essence of the idea is that when a program address gets hot, the sequence of addresses executed immediately following it are likely to be a hot trace. Thus, instead of using complicated path profiling, Dynamo only associates counters with certain special program addresses (such as targets of backward taken branches). When such an address gets hot, the interpreter emits a copy of the interpreted native instructions that immediately follow the one at the hot address. Not only does this provide a statistically likely "hot" trace, but it also allows the trace to be grown past indirect branches and dynamically linked calls. The appeal of this approach is its simplicity and elegance of implementation. In our extensive experiments with alternative region selection schemes, we could never come up with one that matched the performance/overhead ratio of this speculative scheme.

The second innovation is the use of a dynamic trace as the granularity of runtime optimization. The instructions comprising a dynamic trace are often non-contiguous in memory, and thus may not have been part of the static program scope that was available to the generator of the program binary. A dynamic trace is therefore likely to expose new optimization opportunities, even in a statically optimized program binary. Furthermore, Dynamo's traces tend to begin at the targets of backward taken branches, and very often, a cycle of traces is quickly captured within the software code cache by the trace selection scheme. The traces can only be entered at the top,

and they have no control join points within them. This simplicity of control flow allowed us to design a very fast, non-iterative, trace optimizer, that turned out to be highly effective. Dynamo only optimizes each trace once, at the time it is emitted into the software code cache, and does not use any form of "staged optimization". Yet it produces significant performance improvements, even on input programs that were created using high static optimization levels. In our current prototype, the optimizer does not do any instruction scheduling, since the input program already contains scheduled code. Instruction scheduling has the potential of increasing the runtime optimization overhead substantially, depending on the nature of the underlying processor. On the other hand, the time spent within the optimizer is a negligible fraction of the overall Dynamo overhead. If other components of the Dynamo code could be made more efficient, the extra headroom may be sufficient to offset the scheduling overhead.

The third key innovation was our software code cache design. All modern dynamic translators use a software code cache of some sort. However, to the best of our knowledge, all of these implementations size the code cache large enough to avoid the overhead of cache management due to capacity and conflict misses. Thus, multi-megabyte code caches are not uncommon in most dynamic translator implementation. Our approach is exactly the opposite. The Dynamo code cache is sized very small (300 KB in our current implementation), and the system tolerates a significant number of cache flushes. The trick is to do pre-emptive flushing of the software code cache, in anticipation of a working set change. This performs far better than a reactive policy that flushes the cache only on a capacity miss, because the reactive policy often ends up throwing away useful traces in the current working set along with the old traces. This in turn increases the overhead of re-creating the useful traces once again. The code cache design in Dynamo is the principle reason for its small data memory footprint. All internal trace-related data structures in Dynamo are tied to the code cache flush, so that a flush automatically resets all of these memory pools as a side effect.

## 3.4 Bailing out to direct execution

Since performance is an essential goal in our design, Dynamo must avoid situations where there is little likelihood of performance improvement. An advantage that the dynamic optimizer enjoys over other dynamic compilation or dynamic translation systems is the ability to "bail-out", and let the input (native) program execute directly on the underlying processor. Dynamo monitors the ratio of time spent between the software code cache and Dynamo code. When this ratio falls below a threshold, Dynamo bails-out and lets the input program execute directly. Dynamo will also bail out whenever it encounters tricky situations that confuse it.

The disadvantage of bailing out is that our prototype is currently incapable of resuming later on the same program. Once Dynamo bails out, the program continues to execute directly on the processor, and Dynamo never regains control. Since Dynamo has to guard against bailing out too early, it can cause a significant slowdown in very short running programs. In general, a program has to run at least 1.5 mins for our prototype to achieve a speedup or come close to break-even performance through bail-out.

## 3.5 System calls

Dynamo has to examine all system calls in the program code. Usually, this is necessary to avoid losing control over the program, in cases where the kernel might directly invoke a program routine, undercutting Dynamo. An example of this is system calls that install signal handlers. Dynamo intercepts all signal handler installation calls, and substitutes its own handler instead. The kernel will transfer control to Dynamo when the signal arrives, and the program's handler code is then executed under Dynamo control.

Sometimes however, the situation can get quite complicated, and Dynamo has to make a decision on whether it can continue to maintain control over the program without compromising

all the other design goals, such as transparency and performance. An example of this situation is when the program code contains a call to *fork* or *exec*. In principle, it is possible for Dynamo to inject itself into the executable image of the child process, similar to the way the current process was set up to run under Dynamo. Rather than deal with the additional complication this creates however, our prototype will bail out to direct program execution if a *fork* or *exec* is encountered in the program code.

System calls that manipulate the program's resource limits (such as *setrlimit*) present another tricky case. Our approach is to allow calls that increase the program's soft limits, but to bail out if the program code attempts to raise its hard limits.

## 3.6 Self-modifying code

Self-modifying code is code that writes into its own text segment. Self-modification creates a problem, because when a program modifies its own text segment at runtime, it can result in stale program code in Dynamo's software code cache. Fortunately, on the PA-RISC (as well as on most modern microprocessors), the program is expected to explicitly synchronize the processor's instruction cache with the memory image if it writes into its text segment. It does so by invalidating specific lines, or the entire I-cache, forcing it to be re-filled from memory. On the PA-RISC, the *flush* instruction allows invalidation on a line granularity. When Dynamo detects such an instruction in the program code, it immediately flushes the entire contents of the software code cache, so that it gets re-populated with new fragments. This allows Dynamo to even dynamically optimize programs that modify their own text image.

## 4 Memory Layout

An important aspect of our design is that the entire execution of the application program is done under Dynamo control. The original application program instructions never actually execute at their original program text address. Every program instruction is either interpreted by Dynamo or a copy is executed within the software code cache. The same is true of any dynamically linked libraries that may be invoked by the program.

Dynamo thus has to first gain control of the program before the program starts execution. Since transparency is an essential design goal, we have to accomplish this without perturbing the original program's executable image. Otherwise, it will be impossible to ensure precise exception delivery under dynamic optimization (an already difficult task to begin with). We must therefore load the program binary at the same virtual address, whether or not it is going to be dynamically optimized. There are several ways to achieve this, and each has its own pros and cons:

- 1. Modify the kernel loader. Dynamo can be compiled as a shared library that is automatically loaded by the kernel loader when it loads the application program image. The kernel loader then calls the Dynamo entry point instead of the program's main entry point. The advantage of this scheme is that it is truly transparent to the user. The disadvantage is that it requires operating system modification.

- 2. Use *ptrace* to attach to the application program. Ptrace is a mechanism that allows one process to control another, and is typically used by debuggers. Dynamo can be set up as a separate process that attaches to the application program via ptrace, and runs it until the point where *crt0* (the execution start up code at the top of the program's binary image) is about to call the program's entry point. Execution of the application program is then suspended, and Dynamo fetches the program instructions and executes them on its behalf. Like solution 1, this is also transparent, except for the creation of an additional process. The disadvantage of this scheme is its dependence on the ptrace interface. Many operating systems (like embedded RTOSs for example) do not support ptrace.

- 3. Extend the program's text segment in a separate copy of the program executable file. The application program executable file can be copied over to a temporary location, and the program text segment extended by adding the Dynamo text at the end. Then, the *start* symbol (the entry point that is called by *crt0*) is changed to the Dynamo entry point. This new executable file is then *exec*ed. The original program text is still loaded at the same virtual address as it would normally have, but Dynamo will gain control before the actual application program starts. The advantage of this solution is that it does not require modification of any kernel routines, nor does it rely on any special operating system features like ptrace. It is a complete user space solution. The disadvantage is the overhead of doing the file copy (recall that modification of the original program executable file is not an option as per our project design goals).

- 4. Use a special version of *crt0*. Crt0.o is the execution start up code (typically created from the assembly file crt0.s) that is linked in to the executable by the link editor **ld** at link-time. The kernel loader transfers control to the top of crt0 after it has loaded the entire executable image. The crt0 code is responsible for picking up the command line arguments, setting up the initial stack and data segment, and then making a call to the value of the *start* symbol (usually the main() function of the program). Prior to calling the program entry point, crt0 maps the dynamic link loader **dld**, which then loads any dynamically linked libraries (shared libraries) referenced by the application program. A custom version of crt0 can be used to additionally map the Dynamo code (itself compiled as a shared library), and call Dynamo's entry point instead of the one defined by the *start* symbol. The problem with this scheme is that it requires re-linking of the object files that constitute the application program. Solutions 1-3 on the other hand will work with legacy binaries without re-linking. One way to

overcome this problem is to use a special version of **dld**, which loads the Dynamo shared library in addition to any libraries invoked by the program code, and patches the crt0 code so that it jumps to Dynamo's entry point instead of the program's.

All of the above solutions preserve an essential requirement of the transparency goal: they do not modify the application program code. The program instructions generated by the compiler are loaded unmodified into memory. The only modification done is to the execution start up code in *crt0*; and solutions 1 and 2 do not even do this. Furthermore, no re-compilation of the program is necessary, only solution 4 requires re-linking, but using a modified version of **dld** can circumvent this. Note however, that if Dynamo were to be pre-installed in a new system, the system could be shipped with a custom version of crt0.0, preventing the need to re-link binaries created on that system. In this report, we assume solution 4 is used to start up Dynamo.

Figure 2 illustrates a typical memory layout when a program is running under Dynamo control. Dynamo is compiled as a position-independent shared library, allowing several processes running under Dynamo to use a single copy of the Dynamo code. The Dynamo text segment itself can be ROM resident. The Dynamo data segment is process-local, as is the case in any shared library.

Figure 2: Memory layout of a program executing under Dynamo

In contrast to a regular shared library however, Dynamo does not use any part of the program's data segment, including the program's stack or heap. Instead, Dynamo *mmaps* a separate area of memory, which it then manages itself, to allocate its runtime stack and software code cache. No recursive routines are used within Dynamo, and the longest call-chain within Dynamo is known apriori. This allows Dynamo to allocate a fixed amount of room for its runtime stack. Dynamo does not use a malloc-style heap; the separate *mmap*-ed area is used to allocate its dynamic objects, using a custom memory allocator that is part of Dynamo. Thus, Dynamo's operation does not interfere with the application program's runtime stack or heap area in any way, a critical requirement for meeting our transparency goals.

On systems where *mmap* is unavailable (such as in an embedded RTOS), this space has to be statically allocated, for instance by declaring a large enough array to force the bss segment to a certain size. The drawback here is that page-level protection is not possible the way *mmap* allows.

## 4.1 Address space separation

An application program instruction is "executed" only through interpretation, or via direct execution of a copy of it in the software code cache managed by Dynamo. The entire execution of the application program is thus done under Dynamo control. An implication of this is that all application program instructions are actually executed within the same address space as Dynamo. This opens the opportunity for inadvertent or even malicious corruption of the Dynamo data segment (including the contents of the code cache) by the program being dynamically optimized.

The pages containing the Dynamo data segment and the additional *mmap*-ed memory area are marked writeable only when control is within Dynamo. Just before Dynamo transfers control into the software code cache, it sets the protection flags on these pages to be read-only. When control exits the software cache, the original page protections are restored. This prevents any instructions executed within the software code cache from writing into the Dynamo data segments. Dynamo also watches for any system calls in the program that can modify the protection bits associated with a page (such as *mmap*, *munmap*, and *mprotect*). These system calls are always interpreted by Dynamo, and the program code that invokes them is never generated into the software code cache. The interpreter first checks to see if the pages referred to by these calls are outside the Dynamo text and data space. If not, an exception is raised and the system call is not allowed to go through.

Dynamo prevents rogue branches in the program code from jumping into the Dynamo text segment by always trapping control when any branch exits the fragment cache address range<sup>2</sup>. If the exit branch's target address is not within the application program's text segment address range, an illegal address exception is raised.

It is possible that a program branch instruction may target a bad address that coincidentally happens to be within the software cache address space. In the original program its execution would have resulted in an illegal address trap, but when a copy of this instruction is executed within the fragment cache itself, it is legal. Fortunately, this is easily checked, since Dynamo controls the linking of every branch that crosses fragments. At branch linking time (when a fragment is connected to others within the code cache), if the branch target is within the Dynamo text or data segments, Dynamo realizes that this must be a bad address, and the branch instruction is interpreted rather than executed within the fragment cache. The Dynamo interpreter will raise the appropriate exception. This strategy works even for indirect branches whose targets are determined dynamically. For indirect branches, Dynamo generates a jump to a lookup code that is permanently resident in the software code cache. The same check can be performed prior to the lookup.

<sup>&</sup>lt;sup>2</sup> Dynamo can do this because it controls the generation of all code into its fragment cache. A branch whose target is not in the software code cache is made to jump to a special stub that traps control back to Dynamo.

While we have made every attempt to bulletproof our prototype against inadvertent or malicious corruption of the dynamic optimizer system and its code cache, our implementation is not immune from such situations. Having to execute in the same user address space as the program being dynamically optimized creates many obstacles to building a truly robust and transparent system. One could envision Dynamo as eventually becoming a special low-level software layer that is either directly supported by the underlying processor, or is a special operating system service. Such an implementation would allow it to be engineered in a much more transparent and robust manner than was possible in our prototype.

## 5 Control

Figure 3 illustrates the various components of the Dynamo system, and the flow of control between them. The Init component is the main entry point into Dynamo. Control must enter here before any of the application program instructions have started executing. Init is responsible for initializing various internal data structures, and *mmap*-ing space for allocating the Dynamo runtime stack, the software code cache (henceforth referred to as the Fragment Cache), and memory pools for dynamically allocated objects. It then calls the Dispatch component. Dispatch expects to be passed a machine context completely specifying the application program's execution context in the underlying machine, with the value of the PC set to the next executable application program address. Dispatch is the central point of control for the entire Dynamo system. It manages transfer of control between Dynamo and the fragment cache, as well as any exceptions or interrupts that occur when executing within the code cache.

Figure 3: Control flow between the components of the Dynamo system

Dispatch also manages the handshake between the Interpreter and Trace Selector components. When Dispatch is invoked, it first looks up the Fragment Cache for a tag match on the next program PC. If the tag match fails, the Interpreter is invoked. As explained earlier, the Interpreter will interpret until a taken branch, and then return to Dispatch. If the branch target address matches a tag in the Fragment Cache, Dispatch will perform the context switch to transfer control to the cache, else it will invoke the Trace Selector. The Trace Selector is the real "driver" of the Interpreter, controlling the switch that toggles the interpreter's state. The Trace Selector is the place where the actual profiling itself is done. When invoked by Dispatch, the Trace Selector may return immediately after updating a counter associated with the next program PC. Dispatch then invokes the Interpreter again, passing it the return code from the Trace Selector. This Dispatch-Interpreter-Dispatch-Trace Selector-Dispatch loop continues until either (a) a Fragment Cache hit occurs in Dispatch, or (b) a program address gets hot, in which case the Trace Selector

invokes the Fragment Optimizer. The tag information for fragments in the Fragment Cache is maintained in a central data structure in Dynamo memory called the *fragment lookup table*. This is a hash table that is index by a program address, and maps certain program addresses to fragment entry points within the Fragment Cache. Entries are added to this table by the Fragment Linker, just prior to adding a new fragment into the Fragment Cache. The Fragment Cache Manager provides the allocation and deallocation interface to the Fragment Cache, and is responsible for managing the Fragment Cache storage.

### 5.1 Context switches

At any given moment during program execution under Dynamo, control can either be in the Fragment Cache or in the Dynamo code itself. Thus, two different machine contexts exist, one that corresponds to the execution of Dynamo, and the other to the execution of the dynamically generated code in the Fragment Cache. When control is in Dynamo, the underlying machine registers contain Dynamo's context, and the application program's context is kept in a context save area in the Dynamo data segment. When control is transferred to the Fragment Cache, the application program's context is loaded into the underlying machine registers, but Dynamo's context is discarded. Thus, Dynamo never "resumes" execution when control later exits the Fragment Cache. Control always enters Dynamo at the Dispatch entry point when a Fragment Cache exit occurs. Thus the only part of Dynamo's state that needs to be preserved across multiple Fragment Cache entrances is the values of its global data structures. The part of Dynamo's context that is in the machine registers at the time Dynamo is executing is discarded when control is transferred from Dynamo to the Fragment Cache. Thus, there is only *one* context save area maintained by Dynamo, and it is used only for saving the application program's machine state.

The saving and restoring of the program's context is done by Dynamo and not by the underlying operating system. This keeps the context switch fast. However, it can create a vexing problem on some machines. Since the input to Dynamo is a native program binary, we have to assume that all of the user-visible registers in the underlying machine are used by the program code. Unfortunately, on machines that do not have an absolute addressing mode (as is the case with most RISC instruction sets), a spare register has to be created via spilling to the context save area to implement the saving and restoring of the context.

On some systems, it may be possible to compile the Dynamo source program in a mode that restricts Dynamo code to using only a subset of the general-purpose machine registers. This would allow a more lightweight context save and restore sequence, since only those registers that can be modified by Dynamo code need to be saved in the application program's context save area. Another optimization to lower the context switch overhead is to avoid saving and restoring the floating point state of the machine. Dynamo code does not use any floating point, so saving and restoring of the floating-point registers is redundant.

## 5.2 Trapping control

Dynamo has to make sure that when a taken branch exits the Fragment Cache address space, control is not lost. This is accomplished by trapping to Dispatch whenever such a branch is executed. Again, it is inefficient to rely on the operating system to trap control (for instance by using the *break* instruction). For every branch that can exit the Fragment Cache, Dynamo generates a unique linker stub into the Fragment Cache <sup>3</sup>. The branch is modified so that it jumps to its associated linker stub instead of the original target. The code in the linker stub does a branch-and-link to a context save routine, which saves the program context to the context save

<sup>&</sup>lt;sup>3</sup> The linker stubs associated with a fragment are treated as part of the fragment for purposes of storage allocation and de-allocation.

area and then invokes Dispatch. This strategy is similar to that employed in prior dynamic translator implementations, such as Shade [Cmelik and Keppel 1993] and Embra [Witchel and Rosenblum 1996]. Information about the exit branch and its original target address are recorded in a *link record* data structure maintained by the Fragment Linker. The address of this data structure is embedded directly below the branch-and-link instruction in the linker stub corresponding to the exit branch. This "instruction" can never be executed because there is no return corresponding to this branch-and-link instruction.

The location of this embedded link record pointer is automatically communicated to Dispatch via the link register used in the branch-and-link instruction. When Dispatch starts execution, it uses the value of this link register to extract the embedded pointer and retrieve information about the branch that just exited the Fragment Cache. This strategy of directly embedding the pointer in the linker stub avoids the need to implement expensive hashing to achieve the same result. Figure 4 illustrates the scheme used to trap control for branches that would originally have exited the Fragment Cache.

Figure 4: Use of linker stubs to trap control on a Fragment Cache exit

## 5.3 Signal handling

Once Dynamo gains control over the program, it has to maintain it throughout its execution. Signals create a special problem however. If the application program installs its own signal handler, the operating system will transfer control to that handler (located in the program's address space) when the corresponding signal arrives, causing Dynamo to lose control. To prevent this from happening, Dynamo registers its own signal handler (the Signal Handler component in Figure 3) in place of any program-specified signal handlers. The address of the program-specified handler is recorded in an internal table, but the program's signal handler

installation is suppressed. If the signal occurs during execution, control traps to the Dynamo Signal Handler component first, and the program's handler code is then executed under Dynamo control.

Dynamo itself does not arm any signal, so all signals are available to the program running under Dynamo. Nevertheless, our prototype does not do comprehensive signal handling. For instance, there is no guarantee that signals will not get lost, and that signals arriving while executing the program's signal handler under Dynamo control will be handled properly. Further details about signal handling are discussed in the Signal Handler section later in this report.

## 6 Interpreter

The Interpreter component in Dynamo is a *native* instruction interpreter by default. The Interpreter is unique among the Dynamo components because it is designed as a plug-in. The default implementation can be overridden with a different one at Dynamo install time, as long as the plug-in interpreter conforms to certain interface requirements. It can even be a non-native instruction interpreter, allowing Dynamo's dynamic optimization technology to be applied in a variety of situations, such as Java JITs or on-the-fly binary decompression in software. The default interpreter can also be replaced with a hardware native interpreter (i.e., the underlying processor) provided it is capable of supporting the necessary plug-in interface requirements.

## 6.1 Plug-in interpreter interface

The Interpreter's role is to assist Dynamo in profiling the application program for hot spots without having to instrument its loaded binary image, and in collecting the dynamic sequence of native instructions that make up a hot region. The Interpreter supplied to Dynamo must satisfy the following requirements in order to be a valid plug-in:

- 1. It should transfer control to the Trace Selector every time a taken branch interpreted, passing it the PC of the branch instruction and the PC of the taken target. This is the interpreter's "normal state" of operation.

- 2. It should provide a mode of operation in which the *native* form of each interpreted instruction is recorded in a buffer, together with the application program PC that it maps to <sup>4</sup>. When operating in this mode, the Interpreter should call the Trace Selector whenever a taken branch instruction is interpreted, passing it the contents of the buffer (or a pointer to it and its current extent). This is the interpreter's "code generation state".

- 3. Upon return from each of the above calls to the Trace Selector, a return code will specify the state in which the interpreter should subsequently operate.

Figure 5: Handshake between the Interpreter and Trace Selector

\_

<sup>&</sup>lt;sup>4</sup> In the case of a non-native program binary, several native instructions may map to a single program PC.

The Interpreter initially starts up in the normal state. Thereafter, the Trace Selector is responsible for toggling the Interpreter's state via the return code sent back to the Interpreter. The actual profiling itself (i.e., the association of counters with program addresses and incrementing them) is done by the Trace Selector. Figure 5 illustrates the handshake between the Interpreter and the Trace Selector. This handshake is actually done through Dispatch, as discussed earlier in Section 5. Dispatch is only responsible for doing the Fragment Cache lookup upon each return from the Interpreter, and this is not shown in the figure.

The default Interpreter implementation in Dynamo is a straightforward *fetch-decode-eval* loop, where the *eval* part consists of a set of functions written in C to emulate each native instruction opcode. The execution context of the program is updated in Dynamo's context save memory area as a side-effect of interpretation.

## 6.2 Interpretation via just-in-time translation

An alternative implementation is one that uses direct execution on the underlying processor instead of *eval*. This can be implemented by repeatedly doing the following steps:

- 1. Copy a block of program instructions into a buffer.

- 2. Generate additional instructions to trap control when it exits this block of instructions.

- 3. Load the program context from the context save area into the underlying processor registers.

- 4. Jump to the top of the buffered block of instructions, effectively suspending the Interpreter, and starting direct execution of the block on the underlying processor.

- 5. When control exits the block, save the application program context in the underlying processor registers into its context save area, and jump to the interpreter entry point.

Such an interpreter is really using a just-in-time translation mechanism to do the native interpretation. The interpretive overhead involved in these two schemes depends on several factors. Both schemes need to fetch and decode the instructions, the first one for purposes of invoking the appropriate *eval* function, and the second for modifying branch instructions in the block to trap control if they exit the block. The number of interpreter instructions required to evaluate a native instruction in the first scheme is fixed depending on the instruction opcode, and the overall interpretive overhead is directly proportional to the number of instructions interpreted. On the other hand, the second scheme does not involve any "*eval*" step: the instructions are executed directly on the underlying processor. But there is the overhead of the context restore and save to move the program's context between memory and the underlying processor registers upon entry to and exit from the buffered block. In principle, a large enough block of instructions can be fetched into the buffer to offset the overhead of the fetch, decode, context restore and save steps in the second scheme. However, this increases the pressure on the interpreter's fetch mechanism to predict branch directions accurately.

A variation of the second scheme is to make the buffer large enough to hold several blocks. The idea is to treat the buffer as a "transient code cache" that contains code sequences that may become warm, but not quite hot enough to make their way into the main Fragment Cache. This design trades off extra memory space for lower interpretive overhead.

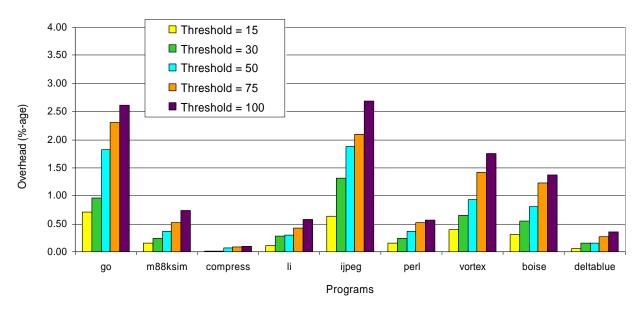

The overall interpretive overhead has a major impact on the design of the Dynamo system. The higher the interpretive overhead, the quicker we want to capture the program's working set within the Fragment Cache, since this code executes directly on the underlying processor. This in turn forces the Trace Selector to be more speculative in its selection of hot spots, since it does not get to observe the program behavior long enough to make a more judicious choice of selecting the hot spots. This has a ripple effect on the Fragment Cache, which now has to compensate for the increased rate of new fragment generation by increasing its size, since frequent replacement can increase Dynamo overhead. The relationship between interpretive overhead (as a percentage of total execution time) and the hot spot selection threshold (how often a program address is encountered before it is considered to be part of a hot region) is shown in Figure 6.

Figure 6: Interpretive overheads

Interpretive overhead can be significantly lowered if the underlying processor (i.e., the native hardware interpreter) can serve as the Dynamo Interpreter. In principle, the underlying processor hardware could itself be used as a plug-in Interpreter, since it is after all an interpreter of the native program code. In order to do so, the hardware may have to be sufficiently enhanced so that it satisfies the Dynamo interpreter plug-in interface. The details of how one might accomplish this are outside the scope of this report.

## 7 Trace Selector

Dynamic optimization is based on identifying hot spots in the executing program. The Trace Selector extracts hot code regions around the detected hot spots and passes them to the Fragment Optimizer for optimization and eventual placement in the Fragment Cache. The arrangement of the extracted hot code regions in the Fragment Cache leads to a new code layout, which has direct impact on future performance of the hot spot code. Furthermore, by passing isolated hot code regions to the Fragment Optimizer, the Trace Selector dictates the scope and kind of runtime optimization that may be performed by the Fragment Optimizer. Thus, the goal of trace selection is twofold: to improve the *code layout* and to expose *dynamic re-optimization* opportunities.

Few new optimization opportunities or improvements in code layout can be expected if the Trace Selector merely copies static regions from the native binary. Regions such as basic blocks or entire procedures are in the static scope of the native program and were already exposed to and possibly optimized by the generator of the native binary. New optimization opportunities are more likely to be found in the dynamic scope of the executing program. Thus, dynamic control flow should be incorporated into the selected code regions.

The code region of choice in Dynamo is a *partial execution trace* (trace for short). Traces fall into the dynamic scope of the native program and directly represent dynamic control flow information. A trace is a dynamic sequence of executed basic blocks. The sequence may not be contiguous in the program memory; it may even be *interprocedural*, spanning one or several procedure boundaries, including dynamically linked modules. Thus, traces are likely to offer opportunities for improved code layout and re-optimization. Furthermore, traces do not need to be computed; they can be inferred simply by observing the runtime behavior of the program through interpretation.

Some profiling is necessary to differentiate hot code region from cold ones. Profile information is collected as a side effect of interpretation, and trace selection is triggered only when a hot program address is interpreted. After selecting a hot trace, the Fragment Optimizer transforms the trace into a location-independent, contiguous code sequence called a *fragment*, which is later placed in the Fragment Cache for execution.

## 7.1 Online profiling

The first task of trace selection is the on-the-fly detection of hot spots. Hot spot detection in the Dynamo context is challenging for two reasons. First, instead of detecting individual hot program points, entire trace information is needed; and second, the profile information is needed *online*. Online profiling is difficult since the profile information is inherently predictive. Hot spots must be detected as they are becoming hot, not afterwards as in conventional offline profiling applications. Furthermore, the profiling techniques must have very low overhead to be of any use as an online technique.

Previously, profiling has commonly been used in an offline manner in feedback systems, such as in profile-based optimization. In such an offline-profile feedback system, a separate profile run of the program is necessary to gather the accumulated profile information that is then fed back to the compiler. There are two conventional approaches to offline profiling: statistical PC sampling and branch or path profiling through static binary instrumentation. Statistical PC sampling [Anderson et al. 1997, Ammons et al. 1997, Conte et al. 1996, Zhang et al. 1997] is an inexpensive technique for identifying hot code blocks by recording program counter hits (i.e., PC samples) at regular time intervals. While PC sampling is efficient for detecting individual hot blocks it provides little help in finding entire hot paths. One could build a hot path by stringing together the hottest blocks, but the individual blocks in such a path may have been hot along entirely disjoint program paths and the resulting path may never execute from start to end.

Another problem with statistical PC sampling is that the timer interrupt signal required to implement it may interfere with programs that arm this signal with a custom handler.

Profiling techniques through binary instrumentation are accurate rather than statistical. However, *branch profiling* techniques suffer the same problem of having to build entire paths from individual branch or block frequencies. Recently proposed *path profiling* techniques offer a way for directly determining the hot paths [Ball and Larus 1996]. The program binary is statically instrumented prior to execution, to collect path frequency information at runtime in an efficient manner. Such path profiling techniques are primarily intended for post-mortem construction of hot path information. The large amount of profile information collected by these techniques, and the overhead of the analysis required to process it, makes them unsuitable for use in a runtime system. Furthermore, instrumenting the program binary perturbs the original program, making it difficult to reach our transparency goal.

Dynamo follows a different approach that is suitable for online profiling. In contrast to traditional profiling methods, the program binary is not instrumented. Rather, interpretation of the program instructions is used to observe its behavior without instrumentation. The profile information gathered via interpretation is consumed as it is produced rather than being used as feedback for a later run.

## 7.2 Speculative trace selection (SPECL)

Dynamo implements a new lightweight profiling strategy by limiting the program points for which execution counts are maintained. The special program points that mark the potential entry of a hot code region are called *trace heads*.

Trace heads are determined as the program executes as the program points that satisfy a *start-of-trace* condition. Since frequently executing code generally involves looping in some form, the start-of-trace condition is satisfied for any program address that is reached via a backward taken branch. Furthermore, hot code regions may extend beyond individual traces. Thus, the targets of branches that exit a previously selected hot trace also meet the start-of-trace criterion. The Trace Selector profiles trace head execution by associating a counter only with the dynamically encountered trace head.

When the Interpreter operates in its normal mode, it always calls the Trace Selector just prior to interpreting the instruction at the start of a trace head. The Trace Selector then increments the counter associated with the trace head, and if the counter exceeds a preset threshold, it toggles the Interpreter's state to trace generation mode (see Figure 5). Since only trace heads are profiled, Dynamo employs a *speculative selection* scheme to form hot traces. The idea here is that when a trace head becomes hot, the sequence of blocks executed immediately following the trace head is statistically likely to be hot. A trace can therefore be grown starting from the hot trace head by simply collecting the subsequently interpreted basic blocks in a history buffer. The scheme is speculative, because it does not use any path profiling information to select the trace.

Once the Trace Selector detects a hot trace head, it toggles the Interpreter's state so that it now operates in a trace generation mode. When executing in the trace generation mode, the Interpreter calls the Trace Selector after each basic block is interpreted. The Trace Selector uses this opportunity to record the sequence of basic block instructions in a history buffer. History collection terminates when the Trace Selector detects an *end-of-trace* condition. An end-of-trace condition occurs when (1) the next block to be executed is identical to the first block in the history buffer (i.e., a cycle), or (2) the current instruction is a backward taken branch (i.e., a new start-of-trace), or (3) the history buffer has reached a size limit.

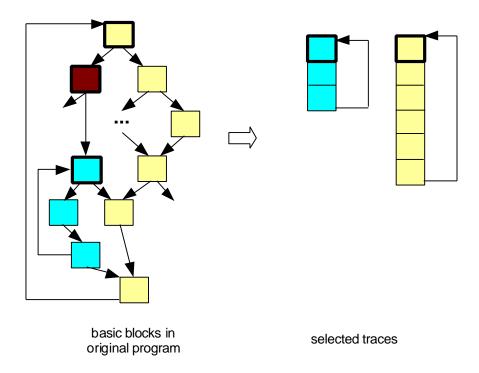

Figure 7: Dynamo's trace selection scheme with trace heads shown in bold

When the end-of-trace condition is satisfied, the trace currently in the history buffer is handed to the Fragment Optimizer. The Fragment Optimizer re-lays out the blocks into a straight-line sequence as shown Figure 7. Finally, before returning to the Interpreter, the Trace Selector toggles its state so that the Interpreter resumes its normal mode of interpretation. At this point, the counter associated with the current trace head is recycled <sup>5</sup>.

Dynamo's speculative trace selection scheme is not only simple, but highly effective as well. This might seem surprising since no path profiling information is used to select the hot traces. The intuition behind the scheme's success is that in program's that have few dominant hot paths the SPECL scheme is statistically very likely to pick one of the dominant paths. On the other hand in program with several competing hot paths, for example program with several hot paths through the same loop, it is not that important which of the competing paths will be picked since the penalty for not picking the truly hottest path cannot be very high.

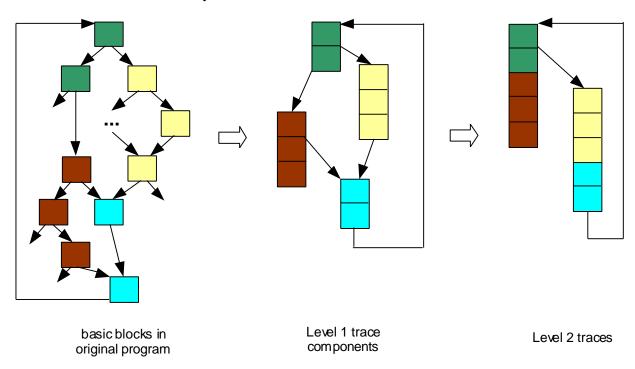

In order to empirically evaluate the effectiveness of our scheme, we compared it against the following three alternative selection schemes. A *basic block selection* scheme, which serves as the base case, a *static selection* scheme that is based on static branch prediction, and a *two-level hierarchical selection* scheme that enhances the static strategy with dynamic execution history information. The three schemes use progressively more sophisticated profiling schemes to detect hot traces. These schemes are discussed here only as a comparison, and in the rest of the paper, unless specifically stated otherwise, the speculative selection (SPECL) scheme should be assumed.

## 7.2.1 Basic block selection (BLOCK)

A basic block scheme is one in which a trace is simply a single dynamic basic block. This is the profiling unit used in early implementations of dynamic translators. A *dynamic basic block* is

<sup>&</sup>lt;sup>5</sup> This is a significant advantage of consuming the profile data on the fly. It is difficult for a static binary instrumentation scheme to mimic this because the profile data is only consumed at the end of the run.

a straight-line code sequence that starts at the target of a branch and extends up to the next branch. Note that unlike conventional static basic blocks, a dynamic basic block may extend across join points. Placing every hot dynamic basic block as an isolated fragment in the Fragment Cache is unlikely to lead to an improved code layout, and hence performance improvement. However, we include basic block selection as a comparison basis for more advanced trace selection schemes.

## 7.2.2 Static trace selection (STATIC)

The static trace selection scheme uses static branch prediction rules [Ball and Larus 1993] to grow traces. Unlike Dynamo's SPECL scheme, the STATIC scheme considers every target of a taken branch as a potential trace head. Correspondingly, execution counts are maintained at every branch target during interpretation. After a branch target has become hot, a static trace is grown as a sequence of basic blocks by repeatedly applying one of the following static branch prediction rules until a branch is encountered for which no rule applies: