# Synthesizing Fine-Grained Synchronization Protocols for Implicit Monitors

KOSTAS FERLES\*, The University of Texas at Austin, USA BENJAMIN SEPANSKI\*, The University of Texas at Austin, USA RAHUL KRISHNAN, The University of Texas at Austin, USA JAMES BORNHOLT, The University of Texas at Austin, USA IŞIL DILLIG, The University of Texas at Austin, USA

A monitor is a widely-used concurrent programming abstraction that encapsulates all shared state between threads. Monitors can be classified as being either *implicit* or *explicit* depending on the primitives they provide. Implicit monitors are much easier to program but typically not as efficient. To address this gap, there has been recent research on automatically synthesizing explicit-signal monitors from an implicit specification, but prior work does not exploit all paralellization opportunities due to the use of a *single* lock for the entire monitor. This paper presents a new technique for synthesizing *fine-grained* explicit-synchronization protocols from implicit monitors. Our method is based on two key innovations: First, we present a new static analysis for inferring *safe interleavings* that allow violating mutual exclusion of monitor operations *without* changing its semantics. Second, we use the results of this static analysis to generate a MaxSAT instance whose models correspond to correct-by-construction synchronization protocols. We have implemented our approach in a tool called Cortado and evaluate it on monitors that contain parallelization opportunities. Our evaluation shows that Cortado can synthesize synchronization policies that are competitive with, or even better than, expert-written ones on these benchmarks.

${\tt CCS\ Concepts: \bullet Software\ and\ its\ engineering \to Concurrent\ programming\ structures; Concurrent\ programming\ languages.}$

Additional Key Words and Phrases: implicit signal monitors, fine-grained locking, concurrent programming, symbolic reasoning, verification conditions, monitor invariant

#### **ACM Reference Format:**

Kostas Ferles, Benjamin Sepanski, Rahul Krishnan, James Bornholt, and Işil Dillig. 2022. Synthesizing Fine-Grained Synchronization Protocols for Implicit Monitors. *Proc. ACM Program. Lang.* 6, OOPSLA1, Article 67 (April 2022), 26 pages. https://doi.org/10.1145/3527311

#### 1 INTRODUCTION

Concurrent programming is difficult because it requires developers to consider interactions between multiple threads of execution and mediate access to shared resources and data. Programming languages can offer higher-level abstractions to reduce this complexity by making concurrent

Authors' addresses: Kostas Ferles, Computer Science Department, The University of Texas at Austin, USA, kferles@cs.utexas.edu; Benjamin Sepanski, Computer Science Department, The University of Texas at Austin, USA, ben\_sepanski@utexas.edu; Rahul Krishnan, Computer Science Department, The University of Texas at Austin, USA, rahulk@cs.utexas.edu; James Bornholt, Computer Science Department, The University of Texas at Austin, USA, bornholt@cs.utexas.edu; Işil Dillig, Computer Science Department, The University of Texas at Austin, USA, isil@cs.utexas.edu.

This work is licensed under a Creative Commons Attribution 4.0 International License.

© 2022 Copyright held by the owner/author(s).

2475-1421/2022/4-ART67

https://doi.org/10.1145/3527311

$<sup>^*\</sup>mbox{Both}$  authors contributed equally to the paper.

programming more declarative. One such abstraction is the *monitor* [Hansen 1973; Hoare 1974], which is an object that encapsulates shared state and allows threads access to it only through a set of *operations*, between which the monitor enforces mutual exclusion.

Ideally, developers would implement monitors using *implicit synchronization*, wherein the *only* synchronization primitive is a waituntil(P) operation that blocks threads until condition P is satisfied. The compiler or runtime can then automatically generate the necessary *explicit synchronization* operations (locks, condition variables, etc.) to implement the monitor in a way that respects the semantics of the implicit monitor. However, automatically deriving an efficient explicit monitor from its implicit specification is a challenging problem, and there have been several recent research efforts, including both run-time techniques like AutoSynch [Hung and Garg 2013] and compile-time tools like Expresso [Ferles et al. 2018], to support implicit-synchronization monitors.

While these state-of-the-art approaches make it possible to program using implicit monitors, they still achieve sub-optimal performance because they adhere closely to the monitor's mutual exclusion requirement. They generally use a *single* lock for the entire monitor and allow access by *at most one* thread at a time across all monitor operations. In practice, however, many monitors can admit additional concurrency while still preserving the *appearance* of mutual exclusion. For example, consider a FIFO queue monitor that provides take and put operations. These two operations can safely run concurrently unless the queue is empty or full, as they will not access the same slot in the queue. Today, realizing this *fine-grained* concurrency requires expert developers to fall back to hand-written explicit synchronization. These implementations are subtle and error-prone, and there is no easy way for developers to determine when they have extracted the maximum possible concurrency from such an implementation.

This paper presents a new technique which automatically synthesizes fine-grained explicit-synchronization monitors. Our technique takes as input an implicit monitor that specifies the desired operations and automatically generates an implementation that allows as much concurrency as possible between those operations while still preserving the appearance of mutual exclusion. The key idea is to decompose each monitor operation into a set of *fragments* and allocate a *set* of locks to each fragment to enforce the mutual exclusion requirement while allowing as many fragments as possible to run concurrently. The resulting implementation selectively acquires and releases locks at fragment boundaries within each operation and signals condition variables as needed.

At a high level, our approach operates in three phases to generate a high-performance explicit synchronization monitor from its implicit version:

- **Signal placement:** First, we use an off-the-shelf technique [Ferles et al. 2018] to infer a signaling regime which determines where to insert signaling operations on condition variables. While the output of this tool is sufficient to synthesize a single-lock implementation, it does not admit any additional concurrency wherein different threads can perform monitor operations simultaneously.

- Static analysis: Second, we perform static analysis to infer sufficient conditions for correctness. That is, the output of the static analysis is a set of conditions such that if the synthesized monitor obeys them, it is guaranteed to be correct-by-construction. A key challenge for this static analysis is to determine which fragments can safely execute concurrently without creating a potential violation of the monitor semantics. The analysis simulates *interleaving* each fragment between the fragments of other operations and determines which possible interleavings are safe.

- Synchronization protocol synthesis via MaxSAT: Finally, we reduce the synthesis problem to a maximum satisfiability (MaxSAT) instance from whose solution an explicit sychronization protocol can be extracted. The hard constraints in the MaxSAT problem enforce the correctness requirements extracted by the static analysis, while the soft constraints encode two competing

objective functions: minimizing the total number of locks used, while maximizing the number of pairs of fragments that can run concurrently.

We have implemented our proposed approach in a tool called Cortado that operates on Java monitors and evaluated it on a collection of monitor implementations that are (1) drawn from popular open-source projects and (2) contain parallelization opportunities that can be achieved via fine-grained locking. Given only the implicit monitor as input, Cortado synthesizes explicit-synchronization monitors that perform as well as, or better than, hand-written explicit implementations by expert developers. Compared to state-of-the-art automated tools for synthesizing explicit monitors [Ferles et al. 2018], Cortado-synthesized monitors extract more concurrency and therefore perform much better (up to 39.1×) on heavily contended workloads.

In summary, this paper makes four main contributions:

- A new technique for automatically synthesizing fine-grained monitor implementations that admit the maximum possible concurrency.

- A novel static static analysis for inferring safe interleaving opportunities between threads.

- A MaxSAT encoding to automate reasoning about *both* the correctness and performance of the synthesized explicit-synchronization monitor.

- An implementation of our technique, CORTADO, that outperforms both state-of-the-art automated tools and expert-written code on benchmarks that can be parallelized via fine-grained locking.

#### 2 OVERVIEW

In this section, we give an overview of our approach through a motivating example. Given the implicit-synchronization monitor shown in Figure 1a, our goal is to automatically synthesize an efficient and semantically equivalent explicit-synchronization monitor like the one presented in Figure 1b. In what follows, we walk through this example and describe how our technique is able to automatically generate the code in Figure 1b.

# 2.1 Implicit-Synchronization Monitor

Our technique takes as input an *implicit-synchronization monitor* that specifies which operations should execute atomically and when certain operations are allowed to proceed but does not fix a specific synchronization protocol for realizing that behavior. For example, Figure 1a shows an implicit monitor that implements a limited capacity blocking queue via a bounded circular array buffer. This monitor defines two operations, put and take, that execute atomically (i.e., the body of each method must appear to execute as one indivisible unit). The put operation adds an object if the queue is not full, and take removes an object if the queue is not empty. If one of these method calls cannot proceed (i.e., queue is full or empty), the monitor blocks the calling thread's execution using a waituntil statement until the operation can be executed. For example, the waituntil statement at line 13 in take blocks execution until there is at least one object in the queue.

As Figure 1a illustrates, implicit-synchronization monitors make concurrent programming simpler because they are *declarative*: they merely state which operations are atomic and when operations can proceed, but they do *not* specify a particular synchronization protocol for realizing that desired behavior. However, most programming languages do not offer implicit synchronization facilities; so, concurrent programs must instead be implemented in terms of *explicit* synchronization constructs such as locks and condition variables, as we discuss next.

### 2.2 Explicit-Synchronization Monitor

Figure 1b shows an explicit-synchronization implementation of the bounded queue from Figure 1a that is written by an expert. This implementation uses two distinct locks, putLock and takeLock,

```

class ArrayBlockingQueue {

1

class ArrayBlockingQueue {

2

int first = 0, last = 0; Object[] queue;

int first = 0, last = 0, count = 0;

AtomicInteger count = new AtomicInteger(0);

2

3

3

Object[] queue;

4

4

5

Lock putLock = new Lock(), takeLock = new Lock();

Condition notFull = putLock.newCondition();

5

ArrayBlockingQueue(int capacity) {

Condition notEmpty = takeLock.newCondition();

6

if (capacity < 1)</pre>

7

7

throw new IllegalArgumentException();

8

// Constructor is the same as the implicit version.

this.queue = new Object[capacity];

9

9

10

void put(Object o) {

10

11

putLock.lock()

11

void put(Object o) {

while (count.get() == queue.length)

// Fragment 1

notFull.await();

12

13

13

waituntil(count < queue.length);</pre>

14

queue[last] = o;

last = (last + 1) %

// Fragment 2

queue[last] = o;

int c = count.getAndIncrement();

15

16

putLock.unlock();

16

// Fragment 3

17

last = (last + 1) %

if (c == 0) {

17

18

// Fragment 4

19

takeLock.lock();

notEmpty.signalAll();

19

count++:

20

takeLock.unlock();}}

20

21

21

22

Object take() {

Object take() {

22

23

// Fragment 5

takeLock.lock();

23

24

while (count.get() == 0)

waituntil(count > 0);

25

24

25

// Fragment 6

26

notEmpty.await();

26

Object r = queue[first];

27

Object r = queue[first];

27

queue[first] = null;

queue[first] = null;

// Fragment 7

first = (first + 1) %

29

28

29

first = (first + 1) %

30

int c = count.getAndDecrement();

// Fragment 8

takeLock.unlock();

if (c == queue.length) {

31

count --:

32

32

return r;

33

putLock.lock();

notFull.signalAll();

33

}

34

35

putLock.unlock();}

34

return r: }}

```

(a) Implicit-synchronization ArrayBlockingQueue.

(b) Explicit-synchronization ArrayBlockingQueue.

Fig. 1. Motivating example.

to protect the put and take methods respectively. The explicit-synchronization monitor also uses an atomic integer for the count field, transforming reads into get() calls (e.g., line 12) and writes into the appropriate atomic method (e.g., count.getAndIncrement() on line 16). The expert-written monitor performs explicit signaling via condition variables notFull and notEmpty that are associated with putLock and takeLock respectively. When a thread cannot execute one of these operations, it calls await on the appropriate condition variable to block its execution (lines 13 and 26). A thread blocked in put can only be unblocked by a corresponding take that frees up space in the queue. To do so, the take must acquire putLock and perform a signal operation on condition variable notFull (lines 33–35). The logic for take is symmetric (lines 19–21).

Although the expert-written version has more locks than a single global-lock implementation, its performance will often be better: Introducing two locks allows put and take to execute concurrently, although multiple concurrent puts are still serialized, as are multiple takes. A single global lock would admit no concurrency in this case and would still incur the same synchronization overhead of acquiring and releasing a lock on every method call. The expert implementation mitigates the overhead of having two locks by acquiring locks selectively: take only acquires the putlock if it is possible for there to be a put operation currently blocked waiting for space in the queue, which happens only if the queue was full when take ran (the put/takelock case is symmetric). This example demonstrates the intricacy of synthesizing fine-grained locking protocols: instead of only minimizing the total number of locks, we must also try to maximize the available concurrency.

### 2.3 Our Approach

Our tool Cortado automatically synthesizes the efficient explicit-synchronization monitor in Figure 1b given the implicit version from Figure 1a. It does so in three phases: First, it infers when and how signaling operations should take place. Second, it performs static analysis to infer sufficient conditions for the synthesized monitor to be correct. Third, it encodes the synchronization protocol synthesis problem as a MaxSAT instance and uses a model of the MaxSAT problem to generate an explicit-sychronization monitor. Since prior work can already handle the first phase, we only focus on the the latter two phases in the following discussion.

*Granularity*. The granularity of our synthesized locking protocol is at the level of *code fragments*, where each fragment is a single-entry region of code within a single method. For example, the fragments chosen for the blocking queue example are indicated by comments in Figure 1a. Fragments are the indivisible unit of concurrency in our approach: we aim to maximize the number of fragments that can run concurrently, but we do not modify the code within a fragment to introduce extra concurrency (e.g., by removing data races). Hence, the explicit monitor synthesized by our approach acquires and releases locks only at fragment boundaries.

*Static Analysis*. To ensure correctness of the synthesized monitor, our technique needs to enforce the following three key requirements:

- (1) **Data-race freedom:** Fragments that involve a data race must not be able to run concurrently.

- (2) **Deadlock freedom:** Locks must be acquired and released in an order that prevents deadlocks.

- (3) **Atomicity:** Each monitor operation should *appear* to take place as one indivisible unit. That is, even though the implementation can allow thread interleavings inside monitor operations, the resulting state should be equivalent to one where each method executes truly atomically.

Here, the second requirement (i.e., deadlock freedom) does not necessitate any static analysis, as we can prevent deadlocks by imposing a static total order  $\leq$  on locks [Birrell 1989] and ensuring that locks are acquired and released in a manner that is consistent with  $\leq$ . However, in order to ensure data-race freedom and atomicity, we need to perform static analysis of the source code to identify (1) code fragments that have a data race, and (2) interleaving opportunities between code fragments. Since detection of data races is a well-studied problem, the novelty of our static analysis lies in identifying safe interleaving opportunities. Hence, the key question addressed by our analysis is the following: Given a code fragment f executed by thread t, and two consecutive code fragments  $f_1$ ,  $f_2$  executed by a different thread t', is it safe to interleave the execution of f in between  $f_1$  and  $f_2$  while ensuring that monitor operations appear to take place atomically?

To answer this question, our method performs a novel static analysis to identify a set of such *safe interleavings*. For instance, going back to the running example, our analysis determines that it is safe to interleave the execution of fragment 4 in Figure 1a in between fragments 5 and 6 by checking a number of commutativity relations between code fragments. In this instance, since our analysis proves that fragment 4 left-commutes [Lipton 1975] with fragment 5 and right-commutes [Lipton 1975] with 6 and all of its successors, we identify this as a safe interleaving opportunity. On the other hand, our analysis concludes that interleaving fragment 4 in between 1 and 2 is *not* safe because fragment 4 does not left-commute with fragment 1 — intuitively, this is because fragment 4 can falsify predicate count < queue.length that appears in the waituntil statement of fragment 1.

**MaxSAT Overview**. Once we identify possible data races and safe interleavings via static analysis, we use this information to generate a MaxSAT instance whose solution corresponds to a fine-grained synchronization protocol. Specifically, our MaxSAT encoding uses a variable  $h_{f_i}^{l_j}$  to indicate that code fragment  $f_i$  must hold lock  $l_j$  and generates both hard constraints (for correctness) and

soft constraints (for efficiency) over these variables. Thus, if the MaxSAT solver returns a model in which variable  $h_{f_i}^{l_j}$  is assigned to true, this means that the synthesized code must acquire lock  $l_j$  prior to executing fragment  $f_i$ . Similarly, our MaxSAT encoding introduces a variable  $a_{fld}$  indicating that field fld should be implemented using an atomic type.

The hard constraints in our MaxSAT encoding correspond to the three correctness requirement mentioned earlier, namely (1) data race prevention, (2) deadlock freedom, and (3) atomicity. On the other hand, soft constraints encode our optimization objective. In what follows, we give a brief overview of the different types of constraints in our encoding, focusing only on constraints that involve lock acquisition variables  $h_{f_i}^{l_j}$ . However, it is worth noting that our technique also generates constraints on atomic variables  $a_{fld}$  and can automatically convert fields to atomic types whenever doing so is safe and more efficient than introducing a lock.

**Data-Race Freedom.** Given a pair of code fragments  $(f_i, f_j)$  that have a potential data race according to the static analysis, our MaxSAT encoding introduces hard constraints of the form  $\bigvee_k (h_{f_i}^{l_k} \wedge h_{f_j}^{l_k})$  stating that  $f_i$  and  $f_j$  must share at least one common lock. For example, in Figure 1a, our analysis determines that fragments 4 and 8 cannot run in parallel since they both write to the same memory location count. Thus, the MaxSAT instance contains boolean constraints to make sure that two different threads cannot execute count— and count++ at the same time.

**Deadlock freedom.** Our approach precludes deadlocks by imposing a total order ≤ on locks. In particular, it enforces that a thread t can only acquire lock l if t does *not* already hold any lock l' where l' < l. For example, in Figure 1a, suppose the locking protocol determines that fragments 1 and 2 must hold all locks in sets  $L_1$  and  $L_2$  respectively. Between executing the two fragments, the code will need to acquire all locks in  $L_2 \setminus L_1$ . Hence, we add constraints i < j for every pair of locks  $l_j \in L_2 \setminus L_1$  and  $l_i \in L_1 \cap L_2$  so that those locks can be acquired while respecting the order ≤.

**Atomicity.** Our MaxSAT encoding also includes constraints to ensure that monitor operations appear to execute atomically. Suppose that our static analysis determines that a thread cannot safely execute code fragment f in between some other thread's execution of code fragments  $f_1$  and  $f_2$ . To prevent such an unsafe interleaving, we add hard constraints to ensure that fragments f,  $f_1$ , and  $f_2$  all share at least one common lock. For example, since our analysis determines that fragment 4 (count++) cannot be interleaved with any other pair of fragments in the same method put (running concurrently on a different thread), our MaxSAT encoding includes a hard constraint asserting that fragment 4 must share a lock with all other fragments in the put method.

**Soft Constraints**. Because the efficiency of the synthesized code depends on both the allowed parallelization opportunities as well as the number of locks, our optimization objective tries to *minimize* the number of locks and *maximize* the number of fragments that can run in parallel. To encode the latter objective, our MaxSAT encoding includes soft contraints asserting that any two parallelizable fragments must *not* share a lock. On the other hand, to encode the former objective, we add a soft constraint stating that no fragment in *m* is holding lock *l*.

*Monitor Generation.* A solution of the generated MaxSAT instance determines (a) which fragments should hold which locks, (b) which fields should be implemented using atomic types, and (c) which locks should be associated with which condition variables. Thus, together with the output of the signal placement technique [Ferles et al. 2018], a model of the MaxSAT problem can be automatically translated into the target monitor implementation. For our running example, Cortado synthesizes precisely the implementation in Figure 1b given the implicit monitor of Figure 1a.

```

Monitor M

:= monitor M \{(fld \mid sync \mid m)^*\}

Field fld

:= \tau f := e

Monitor M

::= monitor M \{(fld \mid m)^*\}

Sync sync

::= Lock l := new Lock()

:= \tau f := e

Field fld

| CondVar cv := l.newCondVar()

Atomic[\tau] a := e

:= m(\vec{v})\{ccr^*\}

Method m

Method m

:= m(\vec{v}) \{ ccr^* \}

CCR ccr

::= waituntil(p); s

CCR ccr

::= (ls)^*

Stmt s

::= skip | v := e | v.f := e

|v.m(\vec{e})| [if (e)]? goto 1

Stmt s

::= skip | v := e | v.f := e

ls_1; ls_2

|v.m(\vec{e})| [if (v)]? goto 1

LStmt ls

::= 1:? s

a_{pre} := a.update(\lambda \chi.e)

(a) Implicit-synchronization monitor language.

LStmt ls

(b) Explicit-synchronization monitor language.

```

Fig. 2. Source & target languages. We use e and p for expressions and predicates respectively.

#### 3 PRELIMINARIES

In this section, we describe our source and target languages and define what it means for an explicit synchronization monitor to correctly implement an implicit one.

### 3.1 Background on Monitors

In this work, we assume that all shared resources between threads are handled by a *monitor class* M which consists of fields F and set of operations (methods) O. The fields F constitute the *only* shared state between threads, which can only access shared state by performing one of the monitor operations  $o \in O$ . These operations can be performed by an arbitrary, yet fixed, number of threads, and locations reachable through arguments are assumed to be thread-local. We represent each thread by a unique identifier from set  $T \subseteq \mathbb{N}$ , and we model memory locations using *access paths* (AP) [Landi and Ryder 1992] of the form  $\pi = v(.f)*$ , consisting of a base variable v optionally followed by a finite sequence of field accesses. We also assume that a special this variable stores the memory location of the monitor object.

*Definition 3.1.* (Monitor State). A monitor state  $\sigma: T \times AP \to \mathbb{N}$  is a mapping from pairs  $(t, \pi)$  (where t is a thread identifier and  $\pi$  an access path) to a value.

### 3.2 Source Language

Our source language, presented in Figure 2a, corresponds to *implicit synchronization monitors* without explicit locking or signaling. The body of each monitor operation consists of a sequence of so-called *Conditional Critical Regions (CCRs)* [Hoare 1971], which in turn consist of a waituntil statement followed by one or more regular non-blocking statements. We refer to the predicate of the waituntil statement of a CCR as its *guard* and to the rest of the statements as its *body*. A thread executes the body of the CCR atomically if its guard evaluates to true; otherwise it suspends its execution and exits the monitor until the predicate becomes true. More formally, the semantics of our source language are defined via the notion of an *implicit monitor history*:

Definition 3.2. (Implicit monitor history). Given a set of threads interacting with each other through monitor  $M_s = (F, O)$ , an implicit monitor history  $h_i$  is a sequence  $(ccr_1, t_1) \dots (crr_n, t_n)$  where each  $ccr_i$  is a CCR of  $M_s$  and  $t_i$  is a thread identifier.

Given history  $h_i$ , we define an *argument mapping*  $v_i$  to be a list whose i'th element maps formal parameters of  $Method(ccr_i)$  to their actual value for each event  $(ccr_i, t_i)$  in  $h_i$ .

Definition 3.3. (Implicit monitor semantics). Given a monitor  $M_s$ , initial state  $\sigma$ , and monitor history  $h_i$  with argument mapping  $v_i$ , the operational semantics of M is defined using a judgment  $M_s \vdash (h_i, v_i, \sigma) \parallel \sigma'$  indicating that the new monitor state is  $\sigma'$  after executing  $h_i$  on state  $\sigma$ .

Because our source language is very similar to the one used in Ferles et al. [2018], we omit a formal definition of the operational semantics. Following that work, we also consider an implicit history to be valid only if it respects the program order of the input monitor.

## 3.3 Target Language

Figure 2b presents the language of explicit-synchronization monitors. The overall structure of this target language is similar to the source language but with a few important differences. First, an explicit monitor contains locks, conditional variables, and atomic fields, collectively referred to as *synchronization variables*. Second, CCRs in the target language do not contain waituntil statements; instead, the logic of a waituntil statement is implemented by calling methods on the appropriate condition variable. We assume that synchronization variables support all the standard synchronization operations present in modern concurrent languages (e.g., await, signal, signalAll, etc.). Finally, our target language contains a special update statement for performing updates on atomic fields: it takes as argument an atomic field a and a unary function f and updates the value of a atomically as f(a). For instance, the statement  $c_{pre} := c.update(\lambda \chi. \chi + 1)$  atomically increments c by one and stores the value of c before the update in  $c_{pre}$ .

Definition 3.4. (Explicit monitor history). Given a set of threads executing in monitor  $M_t = (F, O)$ , an explicit monitor history  $h_e$  is a sequence  $(s_1, t_1) \dots (s_n, t_n)$  where each  $s_i$  is a (non-composite) statement of a monitor operation  $o \in O$  and  $t_i$  is a thread identifier.

Leveraging the same notion of *argument mappings* defined in Section 3.2, we define explicit monitor semantics as follows:

Definition 3.5. (Explicit monitor semantics). Given a monitor  $M_t$ , initial state  $\sigma$ , and monitor history  $h_e$  with argument mapping  $v_e$ , the operational semantics of  $M_t$  is defined using a judgment  $M_t \vdash (h_e, v_e, \sigma) \downarrow \sigma'$  indicating that the new state is  $\sigma'$  after executing  $h_e$  on initial state  $\sigma$ .

The full operational semantics of our target language is given in the extended version of the paper [Ferles et al. 2022].

# 3.4 Relating Implicit and Explicit Histories

In order to formalize the correctness of our approach, we need to relate an implicit history  $h_i$  of a source monitor  $M_s$  with an explicit history  $h_e$  of its corresponding target version  $M_t$ . Because every history of an implicit monitor  $M_s$  induces a corresponding history of its explicit version  $M_t$ , we define an operation called that Expand that "translates" an implicit history to an explicit one. That is, given an implicit history  $h_i$  with argument mapping  $v_i$  and state  $\sigma$ , Expand  $M_t$  ( $h_i$ ,  $v_i$ ,  $\sigma$ ) returns a pair  $h_e$ , where  $h_e$  is a history of  $h_t$  containing all statements executed by  $h_i$  under initial state  $\sigma$  and  $h_t$  is the argument mapping for  $h_t$ .

*Example 3.6.* Consider the implicit monitor of Figure 3a and its explicit counterpart in Figure 3b. For histories  $h_i$  and  $h_e$  from Figure 3c we have Expand<sub> $M_i$ </sub> ( $h_i$ ,  $v_i$ ,  $\sigma$ ) = ( $h_e$ ,  $v_e$ ) for some  $v_i$ ,  $v_e$ .

(a) A simple implicit monitor.

(b) An explicit monitor implementation of Figure 3a.

```

\begin{array}{l} h_i = (foo, t_1)(bar, t_2) \\ h_e = (11. \text{lock}(), t_1)(\text{x++}, t_1)(\text{y++}, t_1)(11. \text{unlock}(), t_1)(12. \text{lock}(), t_2)(\text{z++}, t_2)(12. \text{unlock}(), t_2) \\ h'_e = (11. \text{lock}(), t_1)(\text{x++}, t_1)(12. \text{lock}(), t_2)(\text{y++}, t_1)(\text{z++}, t_2)(11. \text{unlock}(), t_1)(12. \text{unlock}(), t_2) \end{array}

```

(c) Examples of implicit and explicit histories.

Fig. 3. A simple implicit monitor and its explicit implementation.

Using this Expand operation, we can classify explicit histories as being sequential or interleaved:

Definition 3.7. (**Sequential history**) Let  $M_t$  be an explicit monitor implementation of  $M_s$ . We say that an explicit history  $h_e$  of monitor  $M_t$  with argument mapping  $v_e$  is sequential iff there exist a history  $h_i$  of  $M_s$ , argument mapping  $v_i$ , and initial state  $\sigma$  such that Expand  $M_t$ ,  $(h_i, v_i, \sigma) = (h_e, v_e)$ .

In other words, a sequential history corresponds to an execution in which statements of the explicit monitor are not interleaved between threads.

*Example 3.8.* Going back to Figure 3c, history  $h_e$  is sequential but  $h'_e$  is not.

Next, we introduce the notion of *well-formed histories*, which, intuitively, respect the program order of the original implicit monitor:

Definition 3.9. (Well-formed history) Let  $\Pi(h,t)$  be the projection of h onto thread t (i.e., it filters out all elements of h not involving thread t). We say that a history  $h_e$  of  $M_t$  is well-formed iff, for every thread t, there exists sequential histories  $h_e^1, \ldots, h_e^n$  such that  $\Pi(h_e, t) = h_e^1 \cdots h_e^n$ .

Intuitively, well-formed histories respect program dependence in the original monitor for every thread. By definition, every sequential history is also well-formed. In the remainder of this paper, we implicitly mean *well-formed* explicit history whenever we refer to an explicit history.

*Example 3.10.* Histories  $h_e$ ,  $h'_e$  from Figure 3c are both well-formed. However, the following history is not well-formed because it does not respect program order: (12.unlock(), t)(12.lock(), t)

*Definition 3.11.* (Interleaved history) We say that a history  $h_e$  of  $M_t$  is *interleaved* iff it is (1) well-formed and (2) not sequential.

*Example 3.12.* History  $h'_e$  from Figure 3c is interleaved.

Next, we define what it means for an explicit history to simulate an implicit history.

Definition 3.13. (Simulation relation). Let  $M_t$  be an explicit version of implicit monitor  $M_s$ . We say that an explicit history  $h_e$  of  $M_t$  with argument mapping  $v_e$  simulates  $(h_i, v_i)$  of  $M_s$  on input  $\sigma$ , denoted  $(h_e, v_e) \sim (h_i, v_i)$ , if there exist sequential history  $h'_e$  and  $v'_e$  such that:

```

(1) \forall t. \Pi(h_e, t) = \Pi(h'_e, t) and (2) Expand<sub>M<sub>e</sub></sub>(h_i, v_i, \sigma) = (h'_e, v'_e).

```

In other words,  $h_e$  simulates a history of the original monitor if it is a (well-formed) permutation of some sequential history  $h'_e$  of the explicit monitor  $M_t$ .

```

Example 3.14. Going back to Figure 3c, we have (h'_e, v') \sim (h_i, v) for some v, v'.

```

# 3.5 Correctness of Explicit-Synchronization Monitors

Using the concepts introduced in the previous section, we now formalize what it means for an explicit monitor to *correctly implement* an implicit one.

Definition 3.15. (State equivalence) Let  $\sigma$  be a program state of an implicit monitor  $M_s$  and  $\sigma'$  that of an explicit monitor  $M_t$ . We say that  $\sigma$  and  $\sigma'$  are equivalent modulo  $M_s$ , denoted  $\sigma \equiv_{M_s} \sigma'$ , iff for all  $(t, \pi)$  in the domain of  $\sigma$ , we have  $\sigma(t, \pi) = \sigma'(t, \pi)$

Intuitively, this notion of equivalence between two monitor states ignores any additional synchronization fields and local variables introduced by translating M to an explicit-synchronization monitor. Finally, we can define the correctness of an explicit monitor as follows:

Definition 3.16. (Correctness) We say that an explicit monitor  $M_t$  correctly implements an implicit monitor  $M_s$ , denoted as  $M_s \sim M_t$ , iff for all input states  $\sigma_s$ ,  $\sigma_t$  s.t.  $\sigma_s \equiv_{M_s} \sigma_t$ , we have:

$$(1) \ \forall h_i, v_i. \ M_s \vdash (h_i, v_i, \sigma_s) \Downarrow \sigma_s' \Longrightarrow \left( M_t \vdash (\mathsf{Expand}_{M_t}(h_i, v_i, \sigma_s), \sigma_t) \downarrow \sigma_t' \ \land \ \sigma_s' \equiv_{M_s} \sigma_t' \right)$$

$$(2) \ \forall h_e, \nu_e. \ M_t \vdash (h_e, \nu_e, \sigma_t) \downarrow \sigma_t' \Longrightarrow \left( \exists h_i, \nu_i. \ (h_e, \nu_e) \backsim (h_i, \nu_i) \land M_s \vdash (h_i, \nu_i, \sigma_s) \Downarrow \sigma_s' \land \sigma_s' \equiv_{M_s} \sigma_t' \right)$$

The first correctness condition simply states that  $M_t$  does not eliminate any feasible behaviors of  $M_s$ . The second condition, on the other hand, states that every feasible history of  $M_t$  simulates *some* implicit history that results in the same state. Intuitively, this means that all statement interleavings allowed by  $M_t$  provide the illusion that all operations of  $M_s$  are executed atomically.

### 4 MAIN ALGORITHM

In this section, we present our main synthesis algorithm. Specifically, Section 4.1 introduces some preliminary definitions and proves an NP-completeness result to justify the reduction to MaxSAT. Then, Section 4.2 presents the high-level algorithm, Section 4.3 presents the static analysis for inferring safe interleavings, and Sections 4.4 presents the details of the MaxSAT encoding.

# 4.1 Fragment Dependency Graphs and NP-Completeness

Our main synthesis algorithm is parametrized over a partitioning of the input monitor into code fragments, where each code fragment defines a unit of computation that we need to assign locks to. In this section, we clarify our assumptions about these code fragments and prove the NP-completeness of the problem for a given choice of partition.

First, to define what we mean by a valid partition, we represent each method of the monitor as a standard control-flow graph (CFG), where each atomic statement belongs to its own basic block. Given a control-flow graph G and node n, we write Preds(G, n) to indicate the predecessor nodes of n in G and Succs(G, n) to indicate its successors. Then, a valid partition of a method into code fragments is defined as follows:

Definition 4.1. (Partition) Let G = (V, E) be the CFG representation of a method. Then, a partition of this method is a set of CFGs  $\{G_1, \ldots, G_n\}$  with  $G_i = (V_i, E_i)$  such that:

- (1)  $V = \bigoplus_{i=1}^{n} V_i$  and  $E_i = E \cap (V_i \times V_i)$

- (2) For every  $G_i$ , there is at most one node  $n \in V_i$  such that  $Preds(G, n) \nsubseteq V_i$

- (3) Every waituntil(p) statement must belong to its own  $G_i$  i.e., if a node  $n \in V$  is a waituntil statement, then there exists a  $G_i = (\{n\}, \emptyset)$

Intuitively, a *partition* is a set of sub-CFGs such that (1) these sub-CFGs cover all nodes of the original CFG, (2) each sub-CFG has a unique entry node, and (3) waituntil statements belong to their own sub-CFG. We refer to the code snippet represented by each sub-CFG as a *code fragment* and define a notion of *fragment dependency graph (FDG)* as follows:

Definition 4.2. **(FDG)** Given a method m with CFG G = (V, E) and a partition of G into  $\{G_1, \ldots, G_n\}$ , a fragment dependency graph (FDG) is a directed acyclic graph (V', E') such that (1) every  $f_i \in V'$  is the code fragment associated with  $G_i$ ; (2) there is an edge  $(f_i, f_j) \in E'$  iff there is an edge in G from any exit node of  $G_i$  to the entry node of  $G_j$ .

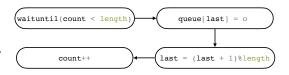

Example 4.3. Figure 4 presents the FDG of method take for the partition in Figure 1a,

Observe that we require the FDG to be acyclic, so some partitions do not give rise to valid FDGs. In the rest of this paper, we assume that partitions obey this restriction so that all cycles are contained within individual nodes of the FDG. We also lift this notion of FDG from individual methods to entire monitors in the obvious way (i.e., union of all FDGs). As we will see in the next section, our synthesis algorithm operates over FDG representations of monitors.

Fig. 4. FDG for method take.

Next, we state the following NP-completeness result to justify our MaxSAT encoding:

THEOREM 4.4. **(NP-Completeness)** Let G = (V, E) be an FDG of monitor M, and let  $\Pi \subseteq V \times V$  be a set of fragment pairs that can run in parallel. Then, deciding whether there exists a synchronization protocol with at most k locks and that allows all pairs in  $\Pi$  to run in parallel is NP-Complete.

PROOF. By reduction from the edge clique cover problem [Michael and Quint 2006]. The proofs of all theorems can be found in the extended version of the paper [Ferles et al. 2022].

# 4.2 Synthesis Algorithm

In this section, we describe our core synthesis procedure, which is summarized in Figure 5. At a high level, the SynthesizeMonitor algorithm consists of the following steps. First, it uses the technique of Ferles et al. [2018] to infer signaling operations (line 4). This yields a partially concretized monitor M' with signaling operations but no locking. Next, it constructs an FDG representation of the resulting monitor M' as defined in Section 4.1 (line 5). Third, it infers an *upper bound*  $N_u$  on the maximum number of locks that the synthesized code should use (line 6). Then, it statically analyzes the FDG to infer requirements that the synthesized code needs to obey (line 7) and uses the results of the previous steps to generate the MaxSAT encoding (line 11). Finally, it instruments M' (line 14) using the synchronization protocol inferred using MaxSAT. Since the most involved aspects of this algorithm are the MaxSAT encoding and inference of safe interleavings, we defer a detailed discussion of these to the next two subsections and focus on the rest.

Iterative Exploration of Lock Count. As mentioned above, our synthesis algorithm conceptually reduces the protocol synthesis problem to MaxSAT and uses an off-the-shelf solver to maximize our optimization objective. To achieve this goal, one option is to generate the MaxSAT encoding based on the maximum possible locks (obtained via the call to ComputeMaxLocks) and then let the solver figure out the optimal number of locks to use. However, in practice, such an approach does not scale because the size of the encoding increases with respect to the maximum number of locks allowed. That is, for many realistic problems, the MaxSAT solver fails to terminate within a reasonable time limit if we generate the encoding based on the maximum possible locks. Thus, instead of directly generating a very large MaxSAT formula up front, our SynthesizeMonitor procedure enters a loop (lines 9–13) wherein it gradually increases the maximum number of locks allowed (and hence the size of the MaxSAT encoding). If we get to a point where the MaxSAT solver starts timing out (indicated by boolean variable called timeout) or we fail to increase the objective

```

1: procedure SynthesizeMonitor(M)

input: M: an implicit-synchronization monitor.

output: a semantically equivalent explicit-synchronization monitor.

3:

4:

M' \leftarrow \mathsf{PlaceSignals}(M)

▶ Use technique of Ferles et al. to infer signaling operations

\mathcal{G} \leftarrow \mathsf{ConstructFDG}(M')

\mathcal{N}_u \leftarrow \mathsf{ComputeMaxLocks}(\mathcal{G})

6:

S \leftarrow \text{StaticAnalyze}(G)

opt \leftarrow -1

8:

for i \in [1, \mathcal{N}_u] do

(\mathcal{H}, \mathcal{S}) \leftarrow \text{MaxSatEncoding}(M, \mathcal{G}, \mathcal{S}, i)

10:

(p, v, timeout) \leftarrow Solve(\mathcal{H}, \mathcal{S})

if timeout \lor (v \le opt) then break

(best, opt) \leftarrow (p, v)

13:

return Intrument(best, G, M')

14:

```

Fig. 5. Main Synthesis Algorithm.

value despite using a larger upper bound on locks (see line 12), then the procedure terminates with the best sychronization policy found so far. While this strategy does not guarantee global optimality, it is much more practical than the alternative.

Signaling Operations. Our synthesis algorithm uses an auxiliary procedure called PlaceSignals [Ferles et al. 2018] which yields a monitor M' that belongs to an intermediate language that is identical to our source language (Figure 2a) except that it contains explicit signaling operations. Specifically, this intermediate language contains two additional signaling directives: (1) signal(p,c) which notifies a single thread that is blocked on predicate p if condition c holds, and (2) broadcast(p,c) which notifies all threads blocked on p if c holds. Figure 6 shows

```

void put(Object o) {

waituntil(count < queue.length);

boolean wasEmpty = count == 0;

queue[last] = o;

last = (last + 1) %

count++;

broadcast(count == 0, wasEmpty);

}</pre>

```

Fig. 6. Method put with explicit signals.

the result of calling PlaceSignals on the put procedure from Figure 1a.

FDG Construction. Recall that an FDG is a generalized version of a control-flow graph where nodes are code fragments rather than basic blocks, and each code fragment is a unit of computation that our algorithm should assign locks to. Since there can be many ways to partition a given method into code fragments, the ConstructFDG procedure invoked at line 5 of Figure 5 implements a particular heuristic for partitioning a method into code fragments. In particular, the more the number of code fragments, the more the parallelization opportunities; thus, our ConstructFDG procedure tries to maximize the number of code fragments while maintaining the invariant that the FDG is acyclic and that each code fragment must have a unique entry point (see Section 5).

**Computing Upper Bound on Locks**. Because the MaxSAT encoding assumes a fixed number of locks, our synthesis algorithm calls the ComputeMaxLocks procedure at line 6 to compute an upper bound on the number of locks needed. Given an FDG  $\mathcal{G} = (V, G)$ , the key idea behind this

procedure is to construct a so-called *conflict graph*  $G_C = (V, E_C)$  where (f, f') is in  $E_C$  iff fragments f and f' have a data race. Since it can be shown that the optimal solution to our problem is an *edge clique cover* [Michael and Quint 2006] of this conflict graph (see extended version [Ferles et al. 2022]), we can use known theorems (e.g., Mantel's theorem, Alon [1986] etc.) to obtain an upper bound on the number of locks needed without having to solve an NP-complete problem.<sup>1</sup>

*Static Analysis.* Recall from Section 2 that the constraints in our MaxSAT encoding utilize information obtained via static analysis. Thus, line 7 of Figure 5 statically analyzes the input monitor to obtain the following three pieces of information:

- Atomic fields  $\mathcal{F}$ : One of the goals of the analysis is to infer a set of fields that could *potentially* be implemented using Atomic types. Thus, our static analysis checks whether (a) a field of type T has a corresponding Atomic T version, and (b) whether all updates to this field can be implemented using one of the methods provided by Atomic T.

- Data races  $\mathcal{R}$ : The second goal of our static analysis is to identify pairs of fragments that would have a data race if they do not use a shared lock. Thus, given a pair of fragments (f, f'), our static analysis checks whether f writes to a memory location l that is accessed in f'.

- Interleaving opportunities *I*: Finally, a third key goal of the analysis is to identify safe interleaving opportunities between fragments. Since this aspect of the analysis is quite involved, we discuss it in the next subsection.

*MaxSAT Encoding*. As mentioned in Section 2, our MaxSAT encoding uses two types of boolean variables, namely (1)  $h_{f_i}^{l_j}$  indicating that fragment  $f_i$  must hold lock  $l_j$  and (2)  $a_f$  indicating that field f should be converted to atomic. Hence, a model of the MaxSAT problem can be easily converted to a so-called *locking protocol*  $(\mathcal{L}, \mathcal{A}, \mathcal{P})$ , where  $\mathcal{L}$  is an assignment from fragments to a set of locks,  $\mathcal{A}$  is a set of fields that should be implemented using atomic types, and  $\mathcal{P}$  is a mapping from waituntil guards to locks. In particular, we have  $l_j \in \mathcal{L}(f_i)$  if and only if  $h_{f_i}^{l_j}$  is assigned to true in the model returned by the MaxSAT solver, and we have  $fld \in \mathcal{A}$  if  $a_{fld}$  is assigned to true. Due to the constraints in our MaxSAT encoding, it is similarly easy to derive  $\mathcal{P}$ : because our encoding ensures that every occurrence of a waituntil(p) statement is protected by the *same* set of locks S, we associate one of the locks l in S with the condition variable introduced for predicate p.<sup>2</sup>

**Instrumentation.** The last step of our algorithm is to synthesize the explicit-synchronization monitor via the Instrument procedure invoked at line 14. Given a synchronization protocol  $(\mathcal{L}, \mathcal{A}, \mathcal{P})$ , the Instrument procedure performs the following steps:

- (1) First, it introduces all the synchronization fields (locks, condition variables, and atomic fields) that appear in the protocol.

- (2) It converts every update to an atomic field to the corresponding atomic update statement.

- (3) Finally, it introduces all the necessary locking and signaling operations to implement the synthesized synchronization protocol.

We refer the interested reader to the extended version of the paper [Ferles et al. 2022] for more details on the instrumentation.

<sup>&</sup>lt;sup>1</sup>In our implementation, we use multiple upper bounds using known theorems and return the best one.

<sup>&</sup>lt;sup>2</sup>Specifically, when choosing which lock l in set S to designate as the representative, we choose the smallest lock in S according to the total order. Because all locks held by a thread must be released before it blocks on a condition variable and must be acquired after it gets notified (with method await releasing and acquiring l internally), choosing the smallest lock prevents deadlocks.

Theorem 4.5. <sup>3</sup>(Correctness) Given an implicit-synchronization monitor M in the language of Figure 2a, if SynthesizeMonitor(M) returns M', then we have  $M \sim M'$ .

# 4.3 Analysis to Identify Safe Interleavings

We now describe how to infer safe interleaving opportunities between threads while ensuring that monitor operations appear to take place atomically. Given a fragment dependency graph  $\mathcal{G} = (V, E)$  for a monitor M, an interleaving opportunity (or interleaving for short) is a pair (v, e) where  $v \in V$  is a code fragment of M and  $e = (v_1, v_2) \in E$  is an edge of the FDG. Intuitively, such an interleaving is safe if some thread can execute v in between some other thread's execution of  $v_1$  and  $v_2$  without violating atomicity. The goal of our static analysis is to identify a set I of such safe interleavings. In what follows, we formalize safe interleavings and describe an analysis for identifying them.

Formalizing Safe Interleavings. To formalize the notion of safe interleaving, we need to keep track of which fragments of the monitor were executed in what order. For this purpose, given an FDG  $\mathcal{G}=(V,E)$  of M, we define a fragmented monitor  $M_{\mathcal{G}}$  to be the same as M except that every fragment in  $\mathcal{G}$  is placed in its own method. Observe that histories of  $M_{\mathcal{G}}$  encode all possible interleavings of fragments in  $\mathcal{G}$ . In this sense, histories of  $M_{\mathcal{G}}$  are similar to explicit monitor histories but are slightly higher level in that they allow interleavings between fragments rather than atomic statements. Thus, we adapt the same notions of sequential, well-formed, and interleaved histories from Section 3.3 to fragmented monitors, as illustrated by the following examples.

Example 4.6. Given monitor M from Figure 1a, its fragmented version  $M_{\mathcal{G}}$  splits put and take into four different methods, each named  $\operatorname{put}_i$  and  $\operatorname{take}_i$ . Given history h=(take,t) and initial state  $\sigma$  with a non-empty queue, we have

$$\mathsf{Expand}_{M_G}(h, v, \sigma) = ((take_1, t)(take_2, t)(take_3, t)(take_4, t), v')$$

where  $take_1, \ldots, take_4$  denote fragments 5-8 in Figure 1a and v, v' are empty argument mappings.

Example 4.7. In the example above, Expand  $M_G(h, v, \sigma)$  is both sequential and well-formed. However,  $(take_1, t)$ ,  $(take_2, t)$  is not well-formed because it does not involve all four methods, and  $(take_1, t)$ ,  $(take_3, t)$ ,  $(take_2, t)$ ,  $(take_4, t)$  is also not well-formed because it executes  $take_3$  before  $take_2$ . Finally, the following history is an interleaved (and, by definition, well-formed) history where threads t and t' execute method take and put respectively:

$$h_G = (put_1, t)(put_2, t)(put_3, t)(take_1, t')(put_4, t)(take_2, t')(take_3, t')(take_4, t')$$

(1)

Furthermore, for this history we have  $(h_{\mathcal{G}}, v_{\mathcal{G}}) \sim ((put, t)(take, t'), v)$  for some  $v_{\mathcal{G}}$  and v. That is,  $h_{\mathcal{G}}$  simulates a history of M where thread t executes method put and t' executes take.

Definition 4.8. (Interleaving) Given an FDG  $\mathcal{G} = (V, E)$  for monitor M, an interleaving is a pair (v, e) where  $v \in V$  and  $e \in E$ . Furthermore, given a history h of fragmented monitor  $M_{\mathcal{G}}$ , we write  $\mathcal{X}(h_{\mathcal{G}})$  to denote the set of all interleavings that occur in h.

*Example 4.9.* For the history  $h_G$  from Eq. 1, we have:

$$X(h_G) = \{(take_1, (put_3, put_4)), (put_4, (take_1, take_2))\}$$

This is the case because this history executes  $take_1$  in between consecutive fragments  $put_3$  and  $put_4$  of some other thread. Similarly, we have  $(put_4, (take_1, take_2)) \in \chi(h_{\mathcal{G}})$  because it executes  $put_4$  in between  $take_1$  and  $take_2$ .

<sup>&</sup>lt;sup>3</sup>All proofs of this Section are in the extended version of the paper [Ferles et al. 2022]

Definition 4.10. (Safe interleavings). Let  $\mathcal{G}$  be an FDG of monitor M. We say that a set of interleavings S is safe, if for every input state  $\sigma$  and every interleaved history  $h_{\mathcal{G}}$  of  $M_{\mathcal{G}}$  we have:

If

$$X(h_G) \subseteq S$$

and  $M_G \vdash (h_G, v_G, \sigma) \Downarrow \sigma'$  then  $\exists h, v. (h_G, v_G) \backsim (h, v)$  and  $M \vdash (h, v, \sigma) \Downarrow \sigma'$

In other words, a set of interleavings S is safe if for every interleaved history of  $h_{\mathcal{G}}$  whose interleavings are a subset of S we can prove that  $h_{\mathcal{G}}$  leads to the same final state as *some* history h of M where h simulates  $h_{\mathcal{G}}$ . This definition essentially lifts the second correctness criterion of Definition 3.16 to a fragmented monitor.

**Inferring Safe Interleavings.** We now turn our attention to the problem of *inferring* safe interleavings. Given a monitor M and its FDG  $\mathcal{G} = (V, E)$ , our goal is to find a set  $I \subseteq V \times E$  such that all interleavings in I are safe. However, a key challenge is that the space of all safe interleavings is exponential (i.e., the power set of  $V \times E$ ), so, even if we had a procedure for checking whether some set I is safe, enumerating all candidates would be computationally intractable.

To overcome this challenge, we introduce the notion of *strong safety* that allows us to build I iteratively. In particular, note that if  $S_1$  and  $S_2$  are both safe interleaving sets according to Definition 4.10, it may *not* be the case that  $S_1 \cup S_2$  is also a safe interleaving. However, to build I incrementally, we need a notion of safe interleaving that is closed under union. For this purpose, we introduce a notion of *strong safety* for a single interleaving (v, e). Since strongly safe interleavings enjoy the property of being closed under union, this notion lends itself to a computationally feasible technique for computing safe interleaving sets. In the remainder of this section, we define strong safety and present our static analysis for computing safe interleaving sets. Towards this goal, we first introduce the notions of *left* and *right commutativity* for our context:

Definition 4.11. (Left/Right Commutativity). Given fragments v and v', we say that v left commutes with v', denoted LeftCommute(v, v'), iff, whenever  $M_{\mathcal{G}} \vdash ((v', t')(v, t), v, \sigma) \Downarrow \sigma'$  holds, so does  $M_{\mathcal{G}} \vdash ((v, t)(v', t'), v, \sigma) \Downarrow \sigma'$ . Conversely, v right commutes with v', denoted RightCommute(v, v'), iff  $M_{\mathcal{G}} \vdash ((v, t)(v', t'), v, \sigma) \Downarrow \sigma'$  implies  $M_{\mathcal{G}} \vdash ((v', t')(v, t), v, \sigma) \Downarrow \sigma'$ .

In other words, a fragment v left commutes with v' if, whenever v executes just after v', the resulting state is the same as if v had executed just before v'. For example,  $f_4$  (i.e. count++) in Figure 1a left-commutes with  $f_5$  since increasing count right after waituntil(count > 0) is equivalent to increasing count just before waituntil(count > 0). That is, assuming that waituntil(count>0) was not blocked before executing count++, then it will still not be blocked after executing count++. However,  $f_4$  does not left-commute with  $f_1$ : when count equals queue.length - 1, incrementing count just after waituntil (count < queue.length) is not equivalent to incrementing queue.length before the waituntil statement. That is, if waituntil(count < queue.length) did not block before executing count++, we cannot guarantee that it also does not block after executing count++.

Next, we use this notion of left and right commutativity to define strong safety:

Definition 4.12. (Strong safety). Let  $\mathcal{G} = (V, E)$  be an FDG for monitor M, and let  $E^*$  denote the reflexive transitive closure of E. We say that an interleaving (v, e), where  $e = (v_s, v_t)$ , is strongly safe if the following conditions are satisfied:

```

(1) \forall v^-.(v^-,v_s) \in E^* \Longrightarrow LeftCommute(v,v^-)

(2) \forall v^+.(v_t,v^+) \in E^* \Longrightarrow RightCommute(v,v^+)

```

That is, an interleaving (v, e) is said to be *strongly safe* if we can prove that fragment v left commutes with *every* possible predecessor of  $v_s$  and that it right commutes with *every* possible successor of  $v_t$ . To see why these conditions imply safety, recall that a set of interleavings S is safe if, for any history  $h_G$  whose interleavings are a subset of S, we can find some (sequential) history

```

1: procedure FINDSAFEINTERLEAVINGS(G)

input: An FDG representation G = (V, E) of monitor M

output: A set \mathcal{I} of all safe interleavings

3:

I \leftarrow \emptyset

4:

for v \in V, e = (v_s, v_t) \in E do

V_s^* \leftarrow \{ v' \mid (v', v_s) \in E^* \}

\triangleright All predecessor vertices that reach v_s.

6:

V_t^* \leftarrow \{ v' \mid (v_t, v') \in E^* \}

\triangleright All successor vertices of v_t.

\mathbf{if} \, \left( \forall v_s^* \in V_s^*. \, \mathsf{LeftCommute}(v, v_s^*) \right) \wedge \left( \forall v_t^* \in V_t^*. \, \mathsf{LeftCommute}(v_t^*, v) \right) \, \mathbf{then}

8:

I \leftarrow I \cup \{(v,e)\}

9:

return I

10:

11: function LeftCommute(v, v')

input: Two fragments v, v'

12:

output: true iff v left commutes with v'

13:

X \leftarrow \{x \mid x \text{ is a variable in } v \text{ or } v'\}.

14:

X_L \leftarrow \{x_l \text{ fresh name } | x \in X\}

X_R \leftarrow \{x_r \text{ fresh name } | x \in X\}

15:

S_L \leftarrow (v'; v)[assume/waituntil, X_L/X] S_R \leftarrow (v; v')[assert/waituntil, X_R/X]

16:

return Verify(\{X_L = X_R\} S_L; S_R \{X_L = X_R\})

17:

```

Fig. 7. Algorithm to find all safe interleavings.

of the original monitor that simulates  $h_{\mathcal{G}}$ . Assuming S contains only strongly safe interleavings, we can create such a sequential history by "removing" interleavings one at a time from  $h_{\mathcal{G}}$ . For instance, let  $\chi = (v, (v_s, v_t)) \in S$  be an interleaving that occurs in  $h_{\mathcal{G}}$ . Since  $\chi$  is strongly safe, we can always obtain an equivalent history  $h_{\mathcal{G}}'$  that has strictly less interleavings than  $h_{\mathcal{G}}$  by commuting v past either every successor of  $v_t$  or every predecessor of  $v_s$  that appears in  $h_{\mathcal{G}}$ .

Example 4.13. For the monitor from Figure 1a, we can show that every interleaving (v,e) where v belongs to method take and edge e belongs to method put (and vice versa) is strongly safe. However, none of the interleavings where v and e belong to the same method are strongly safe. Finally, because both of the interleavings of the history  $h_{\mathcal{G}}$  from Eq. 1 are strongly safe, we can derive a sequential history that simulates history  $h_{\mathcal{G}}$  by swapping  $(take_1,t')$  with  $(put_4,t)$ .

We now state a key theorem that underlies the correctness of our approach:

THEOREM 4.14. Let G be an FDG and let  $\chi_1, \ldots, \chi_n$  be strongly safe interleavings. Then,  $\{\chi_1, \ldots, \chi_n\}$  satisfies Definition 4.10 (i.e., is a safe interleaving set for G).

**Static Analysis Algorithm.** Finally, we conclude this section by presenting our static analysis algorithm (shown in Figure 7) for computing a set I of safe interleavings. At a high level, this algorithm identifies which (v, e) pairs are strongly safe and then returns their union, which by Theorem 4.14, corresponds to a safe interleaving set. To check whether an interleaving (v, e) (for  $e = (v_s, v_t)$ ) is strongly safe, we must check if v left commutes with each predecessor of  $v_s$  and right commutes with each successor of  $v_t$ . As shown in the Left Commute procedure, we reduce

Fig. 8. Inference rules for MaxSatencoding  $(M, \mathcal{G}, \mathcal{S}, \mathcal{N})$  procedure.  $\mathcal{G} = (V, E)$  is an FDG of monitor M,  $\mathcal{S} = (\mathcal{F}, \mathcal{R}, \mathcal{I})$  are the results of the static analysis, and  $\mathcal{N}$  is an upper bound on the number of locks. Predicate IsFrag(v) is true if  $v \in V$ , IsEdge(e) if  $e \in E$ , and SafeInterleaving(v, e) if  $(v, e) \in \mathcal{I}$ . Relations Methods(M) and Preds(M) return all methods of monitor M and all predicates that appear as an argument of a waituntil statement in M respectively.

the verification of left commutativity to the problem of verifying a Hoare triple. In particular, given fragments v, v', we generate a code snippet  $S_L$ ;  $S_R$  where (1)  $S_L$  is an alpha-renamed version of v'; v with waituntil's replaced by assume statements, and (2)  $S_R$  is an alpha-renamed version of v; v' with waituntil's replaced by assert statements. Note that we turn waituntil's in  $S_L$  into assumes because the definition of left commutativity assumes that v'; v has terminated. On the other hand, we need to show that  $S_R$  does not block; thus, we assert that the predicates in the waituntil statement evaluate to true under the assumption that they also evaluate to true in  $S_L$ . Finally, in addition to showing that waituntil's are not blocked, we also need to establish that the monitor state is the same in  $S_L$  and  $S_R$ . Thus, the Hoare triple we construct checks that the values of variables are the same at the end, assuming that they are the same in the beginning. Note that the implementation of right commutativity is the same with v and v' swapped; thus, RightCommute(v, v') can be checked by directly calling LeftCommute(v', v).

# 4.4 MaxSAT Encoding

In this section, we describe our MaxSAT encoding which is formalized as inference rules in Figure 8. Recall that the encoding procedure takes as input (a) an FDG representation of the monitor, (b)

the results of the static analysis, and (c) an upper bound on the maximum number of locks, and it produces a set of hard constraints  $\mathcal{H}$  and a set of soft constraints  $\mathcal{S}$ . In the remainder of this section, we describe the inference rules in Figure 8 for generating these constraints in more detail.

**Variables.** Our MaxSAT encoding uses two types of variables. First, we introduce variables of the form  $h_{v_i}^{l_j}$  indicating that fragment  $v_i$  needs to hold lock  $l_j$ . Thus, given an FDG with n vertices and an upper bound N on the number of locks, our encoding contains  $n \times N$  such variables. The second type of variable used in our encoding is of the form  $a_{fld}$  indicating that fld should be implemented using an atomic type.

*Mutex Encoding.* Given a set of fragments F and an upper bound  $\mathcal N$  on the number of locks, we often need to enforce that all fragments in F share at least one of the  $\mathcal N$  possible locks. We write  $Mutex(F,\mathcal N)$  to denote this requirement. In particular, as shown at the bottom of Figure 8, this is defined as  $Mutex(F,\mathcal N) = \bigvee_{i=1}^{\mathcal N} \bigwedge_{f \in F} h_f^{l_i}$ .

*Hard Constraints.* Next, we describe the hard constraints generated by our MaxSAT encoding. These hard constraints  $\mathcal{H}$  correspond to correctness requirements on the synthesized protocol and include (1) data race freedom, (2) correct signaling and deadlock freedom and (3) atomicity. Specifically, the first two rules in Figure 8 deal with data race freedom, the next rule deals with atomicity, and the last two rules deal with deadlock freedom and correct signaling.

*RACE-1*. The first rule, labeled RACE-1, deals with data race freedom of two fragments that have a data race on a *single* monitor field f. The premises of this rule stipulate that  $v_1, v_2$  are fragments that race *only* on field f which can be converted to atomic (i.e., this.f  $\in \mathcal{F}$ ). In this case, we prevent data races by either (1) enforcing that  $v_1, v_2$  share a lock (the *Mutex* constraint) or (2) ensuring that field f is converted to an atomic field.

*RACE-2.* The next RACE-2 rule prevents data races between fragments where the data race cannot be resolved by making one of the fields atomic. In particular, given two fragments  $v_1$ ,  $v_2$  that have a data race, this rule simply enforces that they share a common lock via the *Mutex* function.

*I-Leave.* The next rule generates constraints to ensure that monitor operations appear to take place atomically. In particular, if the static analysis cannot prove (v,e) to be a strongly safe interleaving (recall Definition 4.12), then we need to ensure that a thread cannot execute v when some other thread is executing e. To do so, we ensure that  $v, v_s, v_t$  all share a common lock by generating a Mutex hard constraint for these three fragments.

L-Order. The next rule, labeled L-Order, ensures that the resulting synchronization protocol is deadlock-free. Specifically, for every edge  $e = (v_s, v_t)$  in the input FDG, this rule generates a hard constraint, via LockOrder(e, N) (defined at the bottom of Figure 8), that ensures that every lock acquisition respects the total order on locks. In particular, for every pair of locks l, u such that l < u, LockOrder(e, N) prevents the synchronization protocol from violating the global order on locks. Recall that a protocol violates this global order if it acquires the "smaller" lock l between  $v_s$  and  $v_t$  while both  $v_s$  and  $v_t$  hold lock u. Thus, the hard constraint generated by LockOrder(e, N) prevents this from happening.

Example 4.15. Assuming

$$\mathcal{N}=2$$

, this rule generates  $\neg\left(h_{v_s}^{l_2} \wedge h_{v_t}^{l_2} \wedge \neg h_{v_s}^{l_1} \wedge h_{v_t}^{l_1}\right)$  for edge  $(v_s,v_t)$ .

*Wait.* The last hard constraint rule, called Wait, is used for associating a single lock with each condition variable. In particular, since all fragments of the form waituntil(p) must hold the same

set of locks, this rule generates two hard constraints for every waituntil predicate p of the input monitor: (1) a mutex constraint for all waituntil(p) fragments and (2) a constraint that enforces that all waituntil(p) fragments must share all common locks.

**Soft Constraints.** As discussed earlier, our goal is to generate a synchronization protocol that is not only correct-by-construction but one that also results in efficient code. Hence, as a proxy metric for efficiency, we want to (1) minimize the number of locks and atomic fields that are introduced, and (2) maximize the number of fragments that can run in parallel. The remaining three rules in Figure 8 introduce soft constraints to encode this optimization objective.

MIN-LOCK. The rule labeled MIN-LOCK is used for minimizing the number of locks. However, instead of simply minimizing the total number of locks used by the protocol, the soft constraints generated by this rule minimize the number of locks used  $per\ method$ . Even though this is not equivalent to minimizing the number of locks used by the entire protocol, we have found this approach to synthesize protocols with a more even distribution of locks among the monitor methods. In practice, such protocols are more desirable because they avoid scenarios where a subset of the methods incur a higher synchronization cost than others. Specifically, this rule generates a soft constraint for every lock  $l \in \{l_1...l_N\}$  and every method m of M and asserts that none of the fragments in m hold lock l.

MIN-ATOM. The MIN-ATOM rule generates soft constrains to minimize the number of fields that are made atomic by asserting that  $a_{fld}$  is assigned to false.

MAX-PAR. The last rule called MAX-PAR generates soft constraints to maximize parallelism. Specifically, for every pair of fragments (v, v') that do not have data races, we add a soft constraint stating that v and v' do not share any locks.

We conclude this Section with a theorem that states the correctness of our MaxSAT encoding.

Theorem 4.16. Let m be a model of the generated MaxSAT instance and  $(\mathcal{L}, \mathcal{A}, \mathcal{P})$  be the synchronization protocol constructed as follows:

$$\mathcal{L} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \; \mathcal{A} = \left\{ \text{fld} \mid m[a_{fld}] \right\} \\ \mathcal{P} = \left\{ p \mapsto l_i \mid IsWait(v, p), i = min(\left\{ j \mid m[h_v^{l_j}] \right\}) \right\} \\ = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\} \\ \mathcal{A} = \left\{ v \mapsto \left\{ l \mid m[h_v^l] \right\} \right\}$$

where, IsWait(v, p) is true if v is a waituntil statement on p. Then,  $(\mathcal{L}, \mathcal{A}, \mathcal{P})$  is a correct synchronization protocol.

### 5 IMPLEMENTATION

We have implemented our approach in a tool called Cortado that emits explicit-synchronization monitors in Java. Cortado is based on the Soot program analysis infrastructure [Vallée-Rai et al. 1999] and the Z3 SMT solver [de Moura and Bjørner 2008]. In particular, we use Soot to perform various kinds of static analyses needed by our method (e.g., pointer analysis) and to translate the input monitor to an explicit-synchronization monitor in Java. Furthermore, we leverage Z3 for solving MaxSAT instances and discharging the validity queries that arise when checking commutativity between fragments. In the remainder of this section, we discuss several design choices and optimizations that were not discussed previously.

**Weights of Soft Constraints.** As expected, the quality of the synthesized protocol depends on the model returned by the MaxSAT solver. In practice, we have observed certain types of soft constraints to be more important than others for efficiency. Thus, our implementation assigns different weights for different classes of soft constraints. For instance, because it is always preferable to use an atomic

field instead of a lock, Cortado assigns a higher weight to soft constraints generated by rule Min-Atom from Figure 8 than the ones generated by rule Min-Lock.<sup>4</sup>

Constructing FDGs. As mentioned in Section 4, Cortado uses a heuristic to partition the input CFG into fragments. The goal of this heuristic is to maximize parallelization opportunities while ensuring that the partition results in a valid FDG according to Definition 4.2. Our heuristic places every loop in its own fragment (to make sure that the FDG is well-formed) and, for code outside loops, Cortado creates a new fragment whenever it detects an update to monitor state (i.e., this.fld = \*). In practice, we found this heuristic to achieve a good balance between the number of parallelization opportunities and the size of the resulting FDG.<sup>5</sup>

Static Analysis Optimization. Our approach uses an off-the-shelf pointer analysis to detect which pairs of FDG fragments do not have a data race (and, so, can run in parallel). However, such an approach, based on pointer analysis alone, often leads to imprecision. For example, Soot's pointer analysis cannot prove that fragments 2 and 6 in Figure 1a do not contain any races, as it does not reason about individual array elements. Therefore, in order to increase the precision of the static analysis, Cortado implements an SMT-based static analysis on top of Soot's built-in pointer analysis and generates appropriate verification conditions (similar to the ones generated by Gurfinkel et al. [2015]) to prove that memory accesses of two fragments are disjoint.

#### 6 EVALUATION

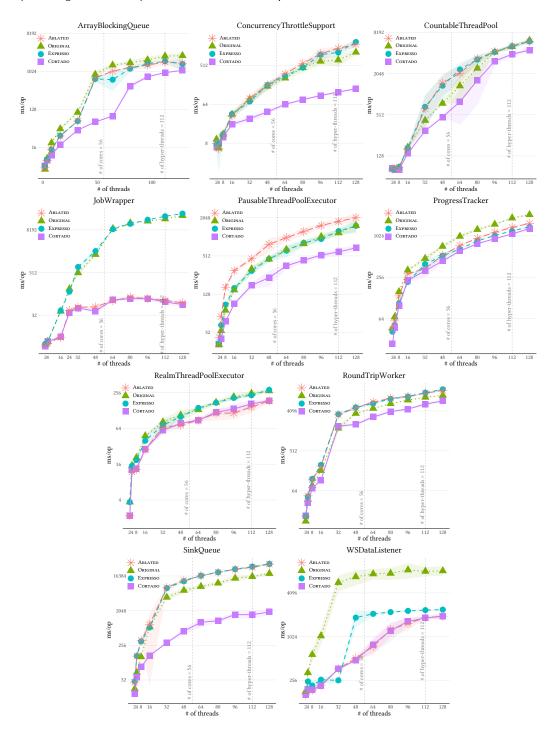

We evaluated CORTADO's ability to generate fine-grained locking protocols by performing a set of experiments that are designed to answer the following research questions:

- **RQ1** How does the code generated by Cortado compare against explicit-synchronization monitors written by experts?

- **RQ2** How does the technique implemented in Cortado compare against other compile-time state-of-the-art approaches targeting implicit-synchronization monitors?

- **RQ3** How does the static analysis for inferring safe interleavings impact the quality of the code generated by Cortado?

- **RO4** How long does Cortado take to synthesize code and how complex are the resulting protocols?

To answer these research questions, we conducted experiments on ten explicit-synchronization monitors from popular open source repositories. Aside from CORTADO, we consider two additional baselines, described below, that aid us in answering our second and third research questions.

Benchmarks. The benchmarks used in our evaluation are collected from popular open source GitHub repositories. We wrote a crawler (based on GitHub's REST API [GitHub 2022]) to automatically identify candidate explicit-synchronization monitors implemented in Java by searching for keywords like lock, unlock, await, etc. We then manually inspected class files returned by the crawler in decreasing order of GitHub popularity (stars and forks) and identified self-contained monitor-style classes that encapsulate shared state accessed by multiple threads. We included such a monitor in our benchmarks only if it satisfies the following conditions: (1) the class has a well-defined API for client threads and (2) it contains parallelization opportunities that can be realized via fine-grained locking. We manually isolated the shared state and monitor methods of the class

<sup>&</sup>lt;sup>4</sup>An ablation study that demonstrates the need for adjusting the weights of soft constraints can be found in the extended version of the paper [Ferles et al. 2022].

<sup>&</sup>lt;sup>5</sup>An ablation study that justifies the design of this heuristic can be found in the extended version of the paper [Ferles et al. 2022]