©Copyright 2012

Laura Effinger-Dean

# Interference-Free Regions and Their Application to Compiler Optimization and Data-Race Detection

Laura Effinger-Dean

${\bf A}$  dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

University of Washington

2012

Reading Committee:

Dan Grossman, Chair

Luis Ceze

David Notkin

Program Authorized to Offer Degree: Computer Science & Engineering

## University of Washington

#### Abstract

Interference-Free Regions and Their Application to Compiler Optimization and Data-Race Detection

Laura Effinger-Dean

Chair of the Supervisory Committee: Associate Professor Dan Grossman Computer Science & Engineering

Programming languages must be defined precisely so that programmers can reason carefully about the behavior of their code and language implementers can provide correct and efficient compilers and interpreters. However, until quite recently, mainstream languages such as Java and C++ did not specify exactly how programs that use shared-memory multithreading should behave (e.g., when do writes by one thread become visible to another thread?). The memory model of a programming language addresses such questions. The recently-approved memory model for C++ effectively requires programs to be "data-race-free": all executions of the program must have the property that any conflicting memory accesses in different threads are ordered by synchronization. To meet this requirement, programmers must ensure that threads properly coordinate accesses to shared memory using synchronization mechanisms such as mutual-exclusion locks.

We introduce a new abstraction for reasoning about data-race-free programs: interference-free regions. An interference-free region, or IFR, is a region surrounding a memory access during which no other thread can modify the accessed memory location without causing a data race. Specifically, the interference-free region for a memory access extends from the last acquire call (e.g., mutex lock) before the access to the first release call (e.g., mutex unlock) after the access. Using IFRs, we can reason sequentially about code that contains synchronization operations. IFRs enable entirely thread-local reasoning, meaning we do not

need to have the whole program available in order to make useful inferences. We develop IFRs as a abstract concept, and also present two practical applications of IFRs.

First, IFR-based reasoning can be used to extend the scope of compiler optimizations. Compilers typically optimize within synchronization-free regions, since the data-race-freedom assumption permits sequential reasoning in the absence of synchronization. We make the observation that this rule of thumb is overly conservative: it is safe to optimize across synchronization calls as long as the calls are interference-free for the variable in question. (We say that a variable is interference-free at a call if the call falls in the interference-free region for an access to that variable.) We have developed two symmetric compiler analyses for determining which variables are interference-free at each synchronization call, thereby allowing later optimization passes to optimize in larger regions that may include synchronization.

Second, we have developed an algorithm for dynamic data-race detection based on the concept of IFRs. Data-race detection is an important problem to the programming languages community: programmers need to eliminate data races during software development in order to avoid costly bugs in production systems. Our algorithm monitors active IFRs for each thread at runtime, reporting a data race if conflicting IFRs in different threads overlap in real time. Conservative approximations of IFRs are inferred using a static instrumentation pass. We compare our algorithm to two precise data-race detectors, and determine that our algorithm catches many data races and provides better performance on most benchmarks.

As a final step, we extend the compiler analyses used in both projects to be interprocedural (i.e., analyzing more than one function at a time). Specifically, we classify functions according to their synchronization behavior, making it easier to infer when IFRs propagate through function calls. On the compiler optimization side, this change means that we can optimize across calls that contain internal synchronization. On the data-race detection side, we are able to statically infer longer IFRs, meaning that we are more likely to detect data races.

# TABLE OF CONTENTS

|           |                                                                           | Page  |

|-----------|---------------------------------------------------------------------------|-------|

| List of I | Figures                                                                   | . iii |

| List of 7 | Tables                                                                    | . vi  |

| Chapter   | 1: Introduction                                                           | . 1   |

| Chapter   | 2: Background                                                             | . 4   |

| 2.1       | Concurrency and Parallelism in Software                                   | . 4   |

| 2.2       | Motivating Memory-Consistency Models                                      | . 13  |

| 2.3       | Programming-Language Memory Models                                        | . 17  |

| 2.4       | Conclusion                                                                | . 27  |

| Chapter   | : 3: Interference-Free Regions                                            | . 28  |

| 3.1       | Interference-Free Regions                                                 | . 28  |

| 3.2       | Formalism                                                                 | . 34  |

| 3.3       | Barriers                                                                  | . 37  |

| 3.4       | Other Applications                                                        | . 43  |

| 3.5       | Conclusion                                                                | . 43  |

| Chapter   | : 4: Intraprocedural Compiler Optimization using Interference-Free Region | s 44  |

| 4.1       | IFR-Based Optimization                                                    | . 44  |

| 4.2       | Algorithm                                                                 | . 46  |

| 4.3       | Data-Race-Freedom                                                         | . 53  |

| 4.4       | Results                                                                   | . 53  |

| 4.5       | Related Work                                                              | . 56  |

| Chapter   | 5: Dynamic Data-Race Detection using Interference-Free Regions            | . 57  |

| 5.1       | Overview                                                                  | . 58  |

| 5.2       | Static Analysis                                                           | . 63  |

| 5.3       | Dynamic Analysis                                                          | . 73  |

| 5.4     | Formalism and Correctness                                                                        | 77 |

|---------|--------------------------------------------------------------------------------------------------|----|

| 5.5     | Evaluation                                                                                       | 79 |

| 5.6     | Related Work                                                                                     | 89 |

| 5.7     | Conclusion                                                                                       | 92 |

| Chapter | 6: Interprocedural IFR Analysis                                                                  | 93 |

| 6.1     | Motivation                                                                                       | 93 |

| 6.2     | Synchronization Behavior                                                                         | 95 |

| 6.3     | Interprocedural Algorithm                                                                        | 96 |

| 6.4     | Compiler Optimization                                                                            | 03 |

| 6.5     | Dynamic Data-Race Detection $\ \ldots \ 1$ | 10 |

| Chapter | 7: Conclusions and Future Work                                                                   | 18 |

# LIST OF FIGURES

| Figure I | Number                                                                                                                                                                                                                                                                                                           | Page |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

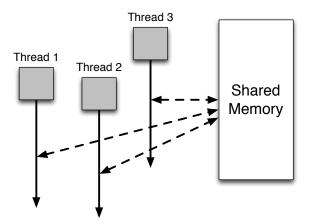

| 2.1      | In shared-memory multithreading, multiple threads of control communicate with each other by reading from and writing to the shared memory. A gray box represents a thread's local memory. The solid lines represent the threads' executions. The dashed lines represent reads of and writes to the shared memory | . 5  |

| 2.2      | A simple bank account application in C                                                                                                                                                                                                                                                                           | . 6  |

| 2.3      | Multithreaded client of the bank account program listed in Figure 2.2                                                                                                                                                                                                                                            | . 7  |

| 2.4      | Possible executions of the multithreaded program listed in Figure 2.3. Note that at most one thread holds b->lock at a time                                                                                                                                                                                      | . 7  |

| 2.5      | Improperly-synchronized version of the bank account program listed in Figure 2.2                                                                                                                                                                                                                                 | . 8  |

| 2.6      | Multithreaded client of the bank account program listed in Figure 2.5                                                                                                                                                                                                                                            | . 9  |

| 2.7      | Two possible executions of the bank account client program listed in Figure 2.6                                                                                                                                                                                                                                  | . 9  |

| 2.8      | An example of thread fork/join. This program spawns (NUM_THREADS - 1) worker threads, then waits for them to complete their tasks                                                                                                                                                                                | . 12 |

| 2.9      | Data-race-free programs must have sequentially-consistent semantics                                                                                                                                                                                                                                              | . 14 |

| 2.10     | Legal compiler optimizations may introduce non-sequentially-consistent behavior                                                                                                                                                                                                                                  | . 15 |

| 2.11     | In safe languages like Java, compiler optimizations must not introduce values out of thin air                                                                                                                                                                                                                    | . 15 |

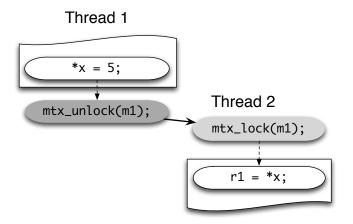

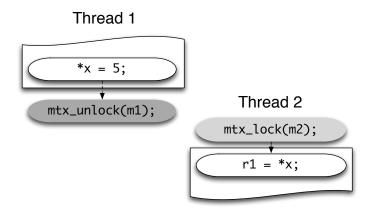

| 3.1      | An interference-free region in a thread trace. Ellipses are synchronization-free code                                                                                                                                                                                                                            | . 31 |

| 3.2      | The interference-free regions for accesses A and C overlap, despite the intervening critical section                                                                                                                                                                                                             | . 31 |

| 3.3      | Here, the load of $p$ at line C means that $p$ is interference-free during both nested critical sections                                                                                                                                                                                                         | . 32 |

| 3.4      | The access at line A is loop-invariant. $\hdots$                                                                                                                                                                                                                                                                 | . 33 |

| 3.5      | Figure 3.4 with the load hoisted out of the loop                                                                                                                                                                                                                                                                 | . 33 |

| 3.6      | A typical use of barriers within a program                                                                                                                                                                                                                                                                       | . 38 |

| 3.7        | Interference-free region around a barrier wait call                                                                                                                                                                                                                              | 41       |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

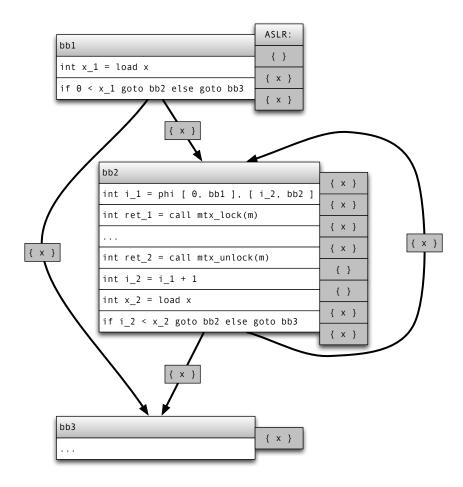

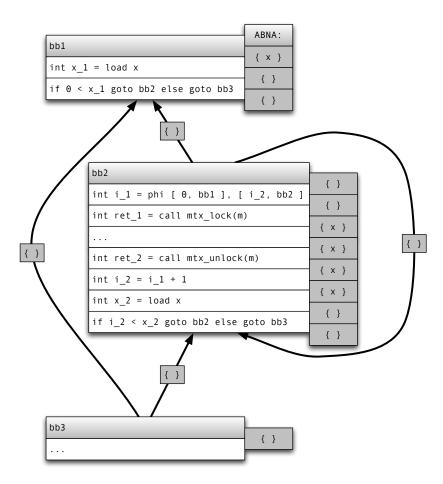

| 4.1<br>4.2 | Subset of LLVM's AliasAnalysis interface related to call side effects Summary of the forwards ASLR analysis used to identify variables that are interference-free at acquire calls. $p'$ is the program point after the statement                                                | 46       |

| 4.9        | at point p                                                                                                                                                                                                                                                                       | 47<br>48 |

| 4.3 $4.4$  | Code for the example in Figures 4.4 and 4.6                                                                                                                                                                                                                                      | 48       |

| 4.4        | Running the ASLR analysis on a program with a loop                                                                                                                                                                                                                               | 49       |

| 4.6        | Running the ABNA analysis on a program with a loop. Since this is a backwards analysis, the control flow edges have been reversed to indicate the direction of data flow.                                                                                                        | 50       |

| 4.7        | A microbenchmark demonstrating the effectiveness of IFR-based optimizations. The microbenchmark uses the pthreads API because C11 threads had not yet been implemented at the time of writing. When combined with our analysis, GVN moves the load of max out of the loop in f() | 54       |

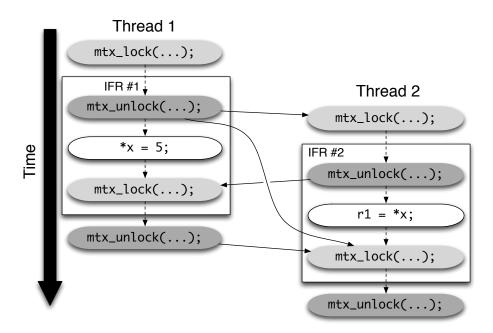

| 5.1        | Overlapping IFRs for racy accesses in an execution. The solid blocks indicate interference-free regions. Dashed lines indicate program order; solid lines indicate possible happens-before edges between synchronization actions. The two accesses must form a data race         | 60       |

| 5.2        | These two accesses do not form a data race, so their IFRs do not overlap                                                                                                                                                                                                         | 61       |

| 5.3        | These two accesses form a data race, even though their IFRs do not overlap.                                                                                                                                                                                                      | 61       |

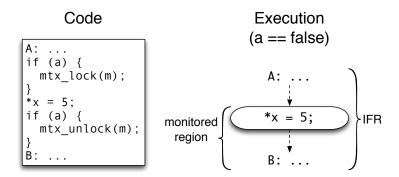

| 5.4        | Monitored regions may be smaller than the actual IFR, due to conservatism in the static analysis                                                                                                                                                                                 | 65       |

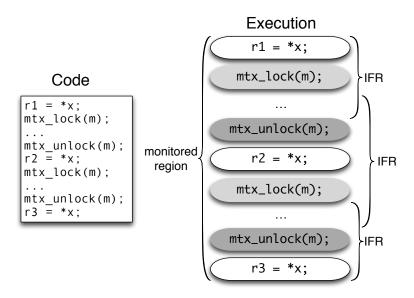

| 5.5        | Monitored regions may combine IFRs for several accesses to the same variable.                                                                                                                                                                                                    | 66       |

| 5.6        | Stopping a monitor too early                                                                                                                                                                                                                                                     | 68       |

| 5.7        | Downgrading a monitor from strong to weak                                                                                                                                                                                                                                        | 68       |

| 5.8        | Summary of our backwards data-flow analysis to insert instrumentation calls. $p'$ is the program point after the statement at point $p$                                                                                                                                          | 71       |

| 5.9        | Even though neither access happens during the other access's IFR, we can detect the race in this case because the accesses' IFRs overlap                                                                                                                                         | 76       |

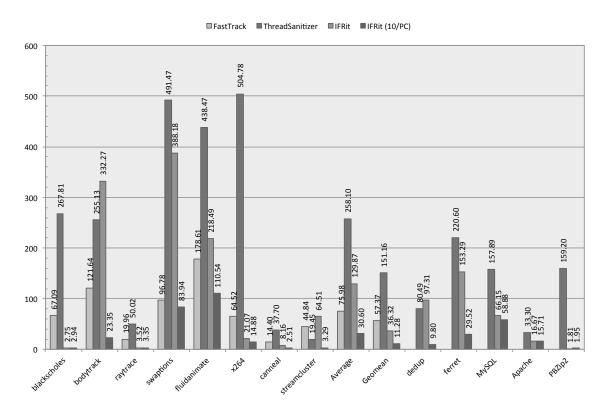

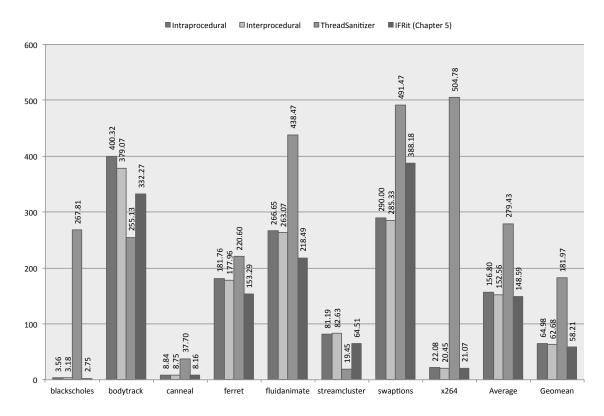

| 5.10       | Overhead of IFRit compared to uninstrumented code for the PARSEC benchmarks and a suite of real applications. Average and geometric mean are over the first eight PARSEC benchmarks                                                                                              | 80       |

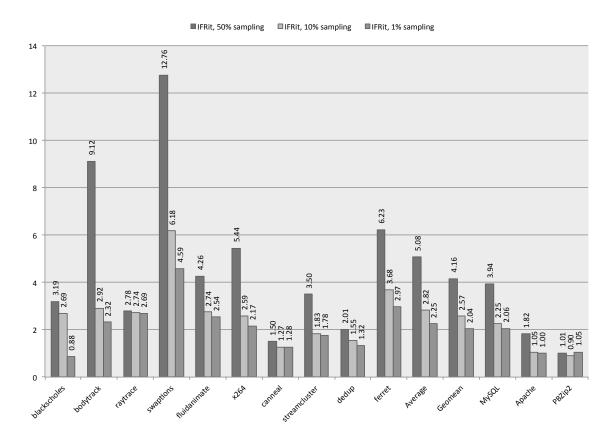

| 5.11       | Effect of sampling on IFRit's performance overhead. Average and geometric mean are over the ten PARSEC benchmarks.                                                                                                                                                               | 81       |

| 6.1  | Example of synchronization behavior in a program                                                                                                                                                                                                |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.2  | Lattice for synchronization behaviors                                                                                                                                                                                                           |

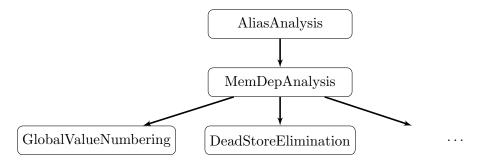

| 6.3  | A subset of the LLVM analysis and optimization pipeline. Arrows indicate information flowing from one analysis to another                                                                                                                       |

| 6.4  | Interface for LLVM's Memory Dependence Analysis                                                                                                                                                                                                 |

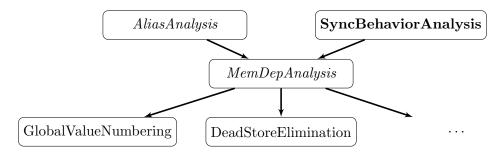

| 6.5  | The LLVM analysis and optimization pipeline, modified to be synchronization-aware. Italicized analyses were modified; bolded analyses are new $107$                                                                                             |

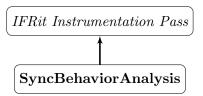

| 6.6  | The IFRit instrumentation pipeline, modified to make use of the synchronization behavior analysis. Italicized analyses were modified; bolded analyses are new                                                                                   |

| 6.7  | The dataflow analysis given in Figure 5.8, modified to use the results of the interprocedural synchronization behavior analysis. $p'$ is the program point after the statement at point $p$                                                     |

| 6.8  | Possible inferred IFRs for a program with an unknown external function call. Possibility #1 assumes that unknown_external has synchronization behavior NONE. Possibility #2 assumes that unknown_external has synchronization behavior ANY      |

| 6.9  | Updated overheads for PARSEC. ThreadSanitizer and IFRit results are repeated from Figure 5.10 for comparison. The average and geomean for ThreadSanitizer and the previous version of IFRit are for the benchmarks included in this figure only |

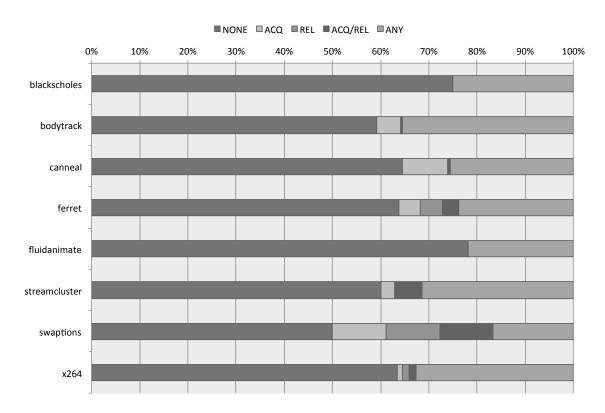

| 6.10 | Distribution of synchronization behaviors for defined functions in the PAR-SEC benchmarks. This distribution is for the case where non-synchronization external functions are assumed to have synchronization behavior NONE 116                 |

# LIST OF TABLES

| Table N | Tumber Page                                                                                                                                                                                                                                                                 |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1     | Synchronization operations                                                                                                                                                                                                                                                  |

| 4.1     | SPLASH-2 results                                                                                                                                                                                                                                                            |

| 5.1     | Number of unique races found by IFRit in various configurations and by ThreadSanitizer. Omitted benchmarks had no detected races 85                                                                                                                                         |

| 6.1     | Bit encodings for synchronization behaviors                                                                                                                                                                                                                                 |

| 6.2     | Results of running LLVM's global value numbering (GVN) pass with the interprocedural synchronization behavior analysis, a modified version of LLVM's GlobalsModRef alias analysis, and the modified version of LLVM's MemDep-Analysis on the SPLASH-2 and PARSEC benchmarks |

| 6.3     | Number of unique races found by the intra- and interprocedural versions of IFRit on PARSEC. ThreadSanitizer results are repeated from Table 5.1 for comparison. Omitted benchmarks had no detected races                                                                    |

## ACKNOWLEDGMENTS

First, I must thank my incredible advisor, Dan Grossman. Dan was always patient and insightful, pushing me to be productive without dictating exactly how I should progress. Thanks, Dan—I am a computer scientist because of you!

Thanks to the other members of my reading committee, Luis Ceze and David Notkin, for their helpful input and advice. Thanks also to Lindsay Michimoto, without whom I probably would not have passed quals, and to Maryam Fazel and Emily Bender, who served as GSR for my general and final exams, respectively.

Thanks to Hans-J. Boehm, my mentor at HP Labs, who convinced me that this "interference-free region" idea was worth investigating.

Thanks to my wonderful family, who asked me relatively rarely when I was going to graduate, and always had confidence that I could succeed. Mom, Dad, and Sean—I love you!

Finally, thanks to my friends in the UW CSE Band, with whom I've had a ridiculous amount of fun over the last six years. At last, I've climbed the "Stairway to Graduation"!

# **DEDICATION**

To the band.

### Chapter 1

## INTRODUCTION

This thesis introduces the concept of *interference-free regions*, and presents two distinct and useful applications of this concept. An interference-free region is a subsection of a single thread's execution surrounding a memory read or write. While a thread is executing an interference-free region, the memory location read or written by the region's defining access cannot be written to by another thread without inducing a *data race*. That is, the two accesses, one in the interference-free region and one in another thread, will not be ordered by synchronization.

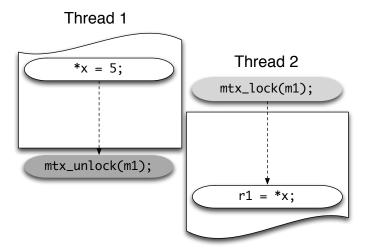

The interference-free region for an access is defined in terms of the synchronization operations surrounding that access in the thread's execution trace. In particular, the interference-free region extends from the first acquire synchronization before the access to the first release synchronization after the access. Acquire synchronizations are operations, like mutex locks, that induce orderings with operations that happened earlier in the execution. Release operations, like mutex unlocks, induce orderings with later operations in an execution.

Interference-free regions are a useful tool for reasoning about data-race-free programs. The latest C and C++ language specifications—C11 [22] and C++11 [23], respectively—require that programs be data-race-free. A program is defined to be data-race-free if all executions of the program have no data races. The reason for this requirement is that various hardware and software optimizations (basically any optimizations that may reorder memory operations) can break a program if the program has data races. Even so-called "benign" data races can lead to very subtle bugs when the program is compiled and executed. Chapter 2 will go into much more detail on the new C and C++ specifications and data-race-freedom.

Chapter 3 formally defines interference-free regions, proves their correctness, and gives illustrative examples. This work began during the author's internship at Hewlett-Packard Laboratories in 2010 and was published at the MSPC workshop in 2011 [14]. In the simplest

case, an interference-free region is simply the innermost critical section enclosing an access. However, if an access does not take place within a critical section, then the interference-free region may include synchronization operations besides the enclosing acquire and release. For example, if a memory location is accessed between two critical sections, then the interference-free region for the access includes both critical sections:

```

mtx_lock(mtx1);

...

mtx_unlock(mtx1);

...

A: r1 = *x;

...

mtx_lock(mtx2);

...

mtx_unlock(mtx2);

interference-free region for A

```

In other words, the location being accessed can be assumed not to be modified by any other threads for the duration of both critical sections. This kind of reasoning, although useful for program optimization, is not used in any standard C and C++ compiler. This leads to the first of two applications for interference-free regions.

Our first application for interference-free regions is *compiler optimization* (Chapter 4): if we may assume data-race-freedom (as we can in C and C++), we can make existing compiler optimizations more aggressive by identifying interference-free regions within the program. (This application was included in the MSPC paper.) For example, suppose two reads of the same memory location x are separated by a mutex lock operation:

```

r1 = *x;

mtx_lock(mtx);

r2 = *x;

```

Normally, the compiler will assume that the mutex lock is a memory barrier, and therefore that another thread could modify the location's value in between the two reads. By reasoning about possible executions of the program, and the interference-free regions for the two reads in those executions, we can determine that any modification of  $\mathbf{x}$  in another thread would be a data race. Therefore the compiler may optimize out the second read. We present two intraprocedural dataflow analyses that refine the modified/reference summaries

for acquire and release synchronization calls, and also discuss how to extend the analyses to handle barrier synchronization.

The second application is dynamic data-race detection (Chapter 5). Programmers use data-race detection tools to find and eliminate bugs in multithreaded programs. However, dynamic data-race detection is very expensive, usually increasing execution time by one or two orders of magnitude. This chapter presents a dynamic data-race detection algorithm based on interference-free regions. The high-level description of the algorithm is that we instrument the code with the beginnings and ends of interference-free regions (building on one of the two algorithms described in Chapter 4), then monitor executions for overlapping, conflicting IFRs. This algorithm permits no false positives and has desirable performance characteristics. In particular, most instrumentation calls require no synchronization. We compare the performance and race detection efficacy of this algorithm to two other race detectors for C and C++. This work will be published at OOPSLA 2012 [15] and is a collaboration with Brandon Lucia, Luis Ceze, Dan Grossman, and Hans-J. Boehm.

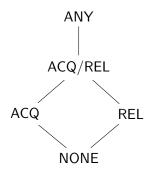

In Chapter 6, we extend the compiler analyses used in Chapters 4 and 5 to be *interprocedural*: analyzing more than one function at a time. The purpose of this extended analysis is to handle functions with internal synchronization correctly. For example, the intraprocedural analyses cannot handle even simple synchronization wrappers, so interprocedural reasoning is necessary to handle more complex programs. The interprocedural analysis does not reason about interference-free regions directly. Instead, it classifies functions according to their synchronization behavior (e.g., no synchronization, only acquire operations, etc.). This information is then used by the previous analyses to produce better results—more optimization opportunities for the analyses in Chapter 4, and more precise interference-free region boundaries for the analysis in Chapter 5.

To summarize, this thesis motivates, defines, and applies the notion of interference-free regions in shared-memory multithreaded programs. We argue that interference-free regions are a useful tool for reasoning about the behavior of data-race-free programs, and support this argument by building and evaluating two applications of interference-free regions. Our contributions improve the state of C and C++ programming in the wake of the new language standards and the increasingly important role of multithreading.

## Chapter 2

#### BACKGROUND

Concurrent programs consist of multiple "threads" working together to accomplish a task, either time-sharing one processor or (for *parallel* programs) using more than one processor at a time. Concurrency is a powerful tool for improving the performance and/or responsiveness of a program by making better use of system resources.

Concurrency is a pressing issue in the programming languages research community. There is a massive body of research on developing concurrency mechanisms, catching concurrent bugs, and so on. Complicating this research is the fact that compiler and hardware optimizations can change the behavior of concurrent programs in surprisingly subtle ways [2, 35, 8]. To fix this problem, we need clear and precise documentation of how a language's concurrency mechanisms affect the language's semantics.

This chapter introduces shared-memory multithreading and gives some relevant background on how concurrency is defined in the language specifications of C, C++, and Java. As we shall see, there are numerous subtle issues that make this problem more difficult than one might expect.

### 2.1 Concurrency and Parallelism in Software

This dissertation is set in the context of *shared-memory multithreading*, a paradigm for writing parallel programs. In shared-memory multithreading, the program has multiple threads of control, each of which has its own stack and registers. Threads communicate by reading and writing memory locations in the shared heap. Figure 2.1 illustrates this idea.

When multiple threads are sharing a resource, it becomes necessary to coordinate the actions of the threads so that they do not conflict with each other. In other words, we need some way of making sure threads are not reading and writing the same memory location at the same time. Programming languages therefore provide various synchronization

Figure 2.1: In shared-memory multithreading, multiple threads of control communicate with each other by reading from and writing to the shared memory. A gray box represents a thread's local memory. The solid lines represent the threads' executions. The dashed lines represent reads of and writes to the shared memory.

mechanisms for coordinating threads.

#### 2.1.1 Mutual-Exclusion Locks

The most common mechanism, and the one we will use for examples throughout this dissertation, is the *mutual-exclusion lock*. Mutual-exclusion locks (called "locks" or "mutexes" interchangeably) are special resources that can be held by at most one thread at a time. A thread can request to hold a lock by calling a *lock acquire* function. Once the thread is granted the lock, it can relinquish it by calling a *lock release* function. We will use the C11 interface for mutual-exclusion locks [22]:

```

#include <threads.h> // type mtx_t defined

int mtx_lock(mtx_t *mtx);

int mtx_unlock(mtx_t *mtx);

```

mtx\_lock acquires the lock argument, blocking until the lock is available; mtx\_unlock releases the lock. Both functions return a code indicating whether the operation succeeded.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>These functions fail only in unusual cases—e.g., if the mutex is configured to be held only by threads of a certain priority and the current thread's priority is too low, or if a thread tries to release a mutex it has not acquired [31].

```

struct BankAccount {

int balance;

mtx_t lock;

...

}

void deposit(struct BankAccount *b, int amt) {

mtx_lock(&b->lock);

b->balance += amt;

mtx_unlock(&b->lock);

}

...

```

Figure 2.2: A simple bank account application in C.

Java, C++, and other languages that support shared-memory multithreading generally provide similar functionality (e.g., Java's synchronized construct).

#### 2.1.2 Example: Bank Account

This section gives a simple example of a multithreaded program, and shows how inter-thread interference can produce unexpected results.

Consider the bank account program shown in Figure 2.2. Here, a bank account is represented by a struct that includes the current balance of the account. The balance is protected by a mutual-exclusion lock; in other words, when a thread reads or writes the balance field, it must first acquire the lock.

Figure 2.3 shows a multithreaded client of the bank account application. Two threads concurrently deposit \$100 each into a bank account with initial balance 0. What are the possible final values of the balance field?

Because the deposit() function accesses the balance only when holding the lock, there are only two possible executions of this program, both listed in Figure 2.4. If Thread 1 gets the lock first, we get execution 2.4a; if Thread 2 gets the lock first, then we get execution 2.4b. Both possible executions result in a final balance of 200. Therefore this is an example of a *properly-synchronized* program—the threads safely coordinate access to the

Initially, b->balance == 0.

| Thread 1         | Thread 2         |

|------------------|------------------|

| deposit(b, 100); | deposit(b, 100); |

(a) Client code.

| Thread 1                                | Thread 2                                |

|-----------------------------------------|-----------------------------------------|

| <pre>mtx_lock(&amp;b-&gt;lock);</pre>   | <pre>mtx_lock(&amp;b-&gt;lock);</pre>   |

| b->balance += 100;                      | b->balance += 100;                      |

| <pre>mtx_unlock(&amp;b-&gt;lock);</pre> | <pre>mtx_unlock(&amp;b-&gt;lock);</pre> |

(b) Client code, with deposit() inlined.

Figure 2.3: Multithreaded client of the bank account program listed in Figure 2.2.

| Thread 1                                | Thread 2                                |

|-----------------------------------------|-----------------------------------------|

| <pre>mtx_lock(&amp;b-&gt;lock);</pre>   |                                         |

| b->balance += 100;                      |                                         |

| <pre>mtx_unlock(&amp;b-&gt;lock);</pre> |                                         |

|                                         | <pre>mtx_lock(&amp;b-&gt;lock);</pre>   |

|                                         | b->balance += 100;                      |

|                                         | <pre>mtx_unlock(&amp;b-&gt;lock);</pre> |

(a)

| Thread 1                                | Thread 2                                |

|-----------------------------------------|-----------------------------------------|

|                                         | <pre>mtx_lock(&amp;b-&gt;lock);</pre>   |

|                                         | b->balance += 100;                      |

|                                         | <pre>mtx_unlock(&amp;b-&gt;lock);</pre> |

| <pre>mtx_lock(&amp;b-&gt;lock);</pre>   |                                         |

| b->balance += 100;                      |                                         |

| <pre>mtx_unlock(&amp;b-&gt;lock);</pre> |                                         |

(b)

Figure 2.4: Possible executions of the multithreaded program listed in Figure 2.3. Note that at most one thread holds b->lock at a time.

```

struct BankAccount {

int balance;

...

}

void deposit(struct BankAccount *b, int amt) {

b->balance += amt;

}

```

Figure 2.5: Improperly-synchronized version of the bank account program listed in Figure 2.2.

shared memory.

Now consider a version of the bank account program that does not properly synchronize accesses to balance. Figure 2.5 lists a version in which the mutex calls have been removed. If we run the client program (Figure 2.6) with this version of the bank account instead, what are the possible values of balance after the execution finishes?

The answer depends on the order in which the two threads access field balance. In Figure 2.6b, we have broken the statement b->balance += 100 into three component steps: (1) reading the value of the memory location corresponding to balance into a temporary variable; (2) adding 100 to the temporary variable's value; and (3) writing the temporary variable's value back to the balance field.

Figure 2.7 shows two of many possible executions. In Figure 2.7a, Thread 1 completes its execution before Thread 2 reads the value of balance, resulting in the expected result of 200. Figure 2.7b shows another possible execution, in which both threads read the value of balance before either thread writes the new value back to balance. In this case, the final value of balance is 100 because both threads see an initial balance of 0.

Therefore this program is erroneous, because (although not formally specified) we expect that depositing 100 twice should result in a net increase of 200. Instead, we found at least one execution where a deposit is "lost." This disparity is an example of how improper synchronization of threads that access the same shared memory location(s) may interfere

Initially, b->balance == 0.

| Thread 1         | Thread 2         |

|------------------|------------------|

| deposit(b, 100); | deposit(b, 100); |

(a) Client code.

| Thread 1                             | Thread 2                             |

|--------------------------------------|--------------------------------------|

| <pre>int tmp1 = b-&gt;balance;</pre> | <pre>int tmp2 = b-&gt;balance;</pre> |

| tmp1 = tmp1 + 100;                   | tmp2 = tmp2 + 100;                   |

| b->balance = tmp1;                   | b->balance = tmp2;                   |

(b) Client code, with deposit() inlined and b->balance += 100 broken into component steps.

Figure 2.6: Multithreaded client of the bank account program listed in Figure 2.5.

| Thread 1                             | Thread 2                             |

|--------------------------------------|--------------------------------------|

| <pre>int tmp1 = b-&gt;balance;</pre> |                                      |

| tmp1 = tmp1 + 100;                   |                                      |

| b->balance = tmp1;                   |                                      |

|                                      | <pre>int tmp2 = b-&gt;balance;</pre> |

|                                      | tmp2 = tmp2 + 100;                   |

|                                      | b->balance = tmp2;                   |

Result: b->balance == 200.

$$(a)$$

| Thread 1                             | Thread 2                             |

|--------------------------------------|--------------------------------------|

| <pre>int tmp1 = b-&gt;balance;</pre> |                                      |

| tmp1 = tmp1 + 100;                   |                                      |

|                                      | <pre>int tmp2 = b-&gt;balance;</pre> |

|                                      | tmp2 = tmp2 + 100;                   |

| b->balance = tmp1;                   |                                      |

|                                      | b->balance = tmp2;                   |

Result: b->balance == 100. (b)

Figure 2.7: Two possible executions of the bank account client program listed in Figure 2.6.

with one another.

#### 2.1.3 Data Races

We say that the executions listed in Figure 2.7 have data races: two threads access a shared memory location (here the balance field) in such a way that the accesses are not ordered by synchronization and at least one access is a write. For example, the statement int tmp1 = b->balance in Thread 1 forms a data race with b->balance = tmp2 in Thread 2. Note that even the "correct" execution in Figure 2.7a has data races (e.g., b->balance = tmp1 races with b->balance = tmp2. This indicates that the execution is, in a sense, broken, even though the memory accesses just so happened to occur in an order that produced the correct answer.

In general, data races should be considered errors, even if they may not always produce an incorrect result. As we have already seen, data races can result in unexpected behavior in the event of unfortunate thread interleavings. In addition, we shall see in Section 2.2 that data races can result in even more insidious errors as a result of unexpected interactions with hardware and compiler optimizations.

## 2.1.4 Synchronizes-With Orderings

When writing multithreaded code, it is important to use proper synchronization such that no possible executions have data races. The program in Figure 2.3 prevents data races using mutual-exclusion locks. Neither of the possible executions in Figure 2.4 have data races, because accesses to balance between the two threads are ordered by synchronization. Formally, we say that a lock release synchronizes-with a later acquire of the same lock. For example, in Figure 2.4a, Thread 1's lock release (mtx\_unlock(b->lock)) synchronizes-with Thread 2's lock acquire (mtx\_lock(b->lock)). This ordering between the unlock and lock actions induces a partial ordering over the memory accesses in the two threads: all the actions in Thread 1's execution "happen before" the actions in Thread 2.

This concept of synchronizes-with orderings extends to types of synchronization beyond mutual-exclusion locks. In general, we say that any synchronization operation that

| Operation    | Synchronization type |

|--------------|----------------------|

| mtx_lock     | Acquire              |

| mtx_unlock   | Release              |

| thrd_create  | Release              |

| thrd_join    | Acquire              |

| atomic_store | Release              |

| atomic_load  | Acquire              |

Table 2.1: Synchronization operations.

synchronizes-with earlier operations is an acquire operation (e.g., mtx\_lock is an acquire operation because it synchronizes-with earlier release operations). Acquire operations induce orderings on the operations in the same thread that come after the acquire. Similarly, any synchronization operation that synchronizes-with later operations is a release operation (e.g., mtx\_unlock). Release operations induce orderings on the operations in the same thread that come before the release.

The next few sections will have more examples of acquire and release operations; Table 2.1 lists the operations we will discuss and their synchronization types.

## 2.1.5 Thread Fork and Thread Join

Java, C and C++ all use the same language mechanism to create threads: a special *fork* operation that spawns a new thread. In C11, the fork operation is a library function with the following signature [22]:

```

#include <threads.h> // defines thrd_t and thrd_start_t

int thrd_create(thrd_t *thr, thrd_start_t func, void *arg);

```

Here thr is a pointer to the thread ID (initialized by thrd\_create), func is the function for the new thread to execute, and arg is the argument to pass to the function.

The thread fork operation synchronizes-with the first operation of the newly-created thread. Therefore thread fork is a *release* operation: it induces ordering on operations that came before it. Practically, this means that a thread can initialize shared state before

```

int worker(void *arg) {

int me = (int) arg;

... // do work

}

int main() {

thrd_t tids[NUM_THREADS];

for (int i = 1; i < NUM_THREADS; i++) {

thrd_create(&tids[i], worker, (void *) i);

}

worker(0);

for (int i = 1; i < NUM_THREADS; i++) {

int res;

thrd_join(tids[i], &res);

}

... // process result

}</pre>

```

Figure 2.8: An example of thread fork/join. This program spawns (NUM\_THREADS - 1) worker threads, then waits for them to complete their tasks.

forking off threads, and those initialization writes will not conflict with reads or writes in spawned threads.

Joining a thread means waiting for the thread to complete. This is useful, for example, if the main thread forks several worker threads, and needs to aggregate their results once all threads have finished (a model typically called fork/join parallelism). C11 supports thread join as follows:

```

#include <threads.h> // defines thr_t

int thrd_join(thrd_t thr, int *res);

```

thr is the thread ID and res is where the return value of the thread is stored. thrd\_join synchronizes-with the end of the joined thread, so it is an acquire operation.

Figure 2.8 gives a simple example of a multithreaded program that uses fork/join parallelism to farm out a large task to worker threads.

#### 2.1.6 Volatile Variables

The last type of synchronization we will discuss, available in Java, C and C++, is *volatile* variables. By definition, concurrent accesses to volatile variables do not constitute a data race. In C and C++, volatile variables are called *atomics*. They have the following interface (here specialized for integers, but available for many types):

```

#include <stdatomic.h> // defines atomic_int, atomic_long, ...

void atomic_store(volatile atomic_int *object, int desired);

int atomic_load(volatile atomic_int *object);

```

Volatile loads synchronize-with previous volatile stores to the same location. Therefore volatile loads are acquire operations and volatile stores are release operations.

## 2.2 Motivating Memory-Consistency Models

In order to make these concurrent features usable by programmers, they must be integrated into the specification of the language such that the semantics of concurrent programs are well-defined and straightforward to reason about. A memory-consistency model (or memory model) is the component of the language specification that defines how threads interact through shared memory. In particular, the memory model defines which values may be returned by read operations. Memory models were originally defined at the hardware level; we do not discuss hardware models in detail and instead refer the reader to Adve and Gharachorloo's tutorial [2].

The strongest, most intuitive semantics for multithreaded programs is sequential consistency, originally described by Lamport [25]. Sequential consistency requires that the memory actions of each thread be interleaved in a total order consistent with the program order in each thread, such that a read always sees the most recent write to the same location in this total order. From the programmer's perspective, sequential consistency is the easiest semantics to reason about and provides the optimal level of programmability. However, modern high-level programming languages have sophisticated compilers that rely on complex code transformations to achieve good performance. These code transformations may reorder memory operations, potentially violating sequential consistency. Ubiquitous optimizations like common subexpression elimination and hoisting operations out of loops are

Initially, x == 0 and y == 0.

| Thread 1     | Thread 2     |

|--------------|--------------|

| r1 = x;      | r2 = y;      |

| if (r1 != 0) | if (r2 != 0) |

| y = 42;      | x = 42;      |

r1 == 42 and r2 == 42 is illegal.

Figure 2.9: Data-race-free programs must have sequentially-consistent semantics.

essentially forms of memory reordering. Therefore, modern languages have adopted *relaxed* memory-consistency models, which provide weaker guarantees than sequential consistency so that key compiler optimizations are legal.

The memory-consistency model of a language acts as a contract between the programmer and the compiler. The approach taken by the vast majority of models is for *correctly synchronized* code to behave as if the language supported sequential consistency, while *incorrectly synchronized* programs may have weaker semantics. A program is correctly synchronized if no sequentially consistent executions of the program have data races (i.e., two threads accessing the same location at the same time where at least one access is a write). As long as a program is data-race-free, the compiler guarantees that any optimizations will not change the semantics of the program. This compromise, called the *data-race-free guarantee*, exploits the fact that most compiler optimizations are safe for data-race-free programs. Specifically, compilers must avoid optimizing across synchronization calls or introducing new data races.

For example, consider the program in Figure 2.9 (reprinted from the Java Memory Model paper [35]). Although the program contains writes to x and y, they will never occur in a sequentially consistent execution of the program. Therefore the program is data-race-free, and the only legal outcome is r1 == 0 and r2 == 0. The compiler must be careful not to move either write earlier, because such a transformation could violate the semantics of the program.

In the last decade, three popular mainstream languages have defined precise memory-

Initially, x == 0 and y == 0.

| Thread 1 | Thread 2 |

|----------|----------|

| r1 = x;  | r2 = y;  |

| y = 1;   | x = r2;  |

r1 == 1 and r2 == 1 is legal.

Figure 2.10: Legal compiler optimizations may introduce non-sequentially-consistent behavior.

Initially, x == 0 and y == 0.

| Thread 1 | Thread 2 |

|----------|----------|

| r1 = x;  | r2 = y;  |

| y = r1;  | x = r2;  |

Incorrectly synchronized, but we want to disallow r1 == 42 and r2 == 42.

Figure 2.11: In safe languages like Java, compiler optimizations must not introduce values out of thin air.

consistency models: Java [35, 19], C, and C++ (both of which use the same underlying model) [11, 22, 23]. The existence of these two models, as well as the considerable community effort that went into developing both of them, stresses the importance of this problem. Both models take the data-race-free approach to provide programmability while also allowing reasonable compiler optimizations. Given that both models support the data-race-free guarantee, the differences between the two models define a clear design space. The Java memory model must support Java's strong language guarantees of security and safety. Therefore the model provides reasonably strong semantics even to programs that are not correctly synchronized. C++ is an unsafe language, so its model does not define any semantics for incorrectly synchronized programs, focusing instead on simplicity and flexibility. The C++ model has the advantage of having a concise specification, as well as allowing more compiler optimizations than Java. We discuss these and other models in Section 2.3.

## 2.2.1 Compiler Optimizations

We illustrate how compiler optimizations can affect the semantics of multithreaded programs via two simple examples. Consider the program shown in Figure 2.10, which is reprinted from the JMM paper [35]. Here x and y are shared variables, and r1 and r2 are local variables. In a sequentially consistent language, the outcome r1 == 1 and r2 == 1 is not legal, because at least one of the reads must execute before either of the writes. But an optimizing compiler may reorder independent operations in a single thread; if the compiler reorders the read and the write in Thread 1, the outcome r1 == 1 and r2 == 1 is possible. Because this optimization is entirely standard and the spurious result does not violate any safety guarantees, this example should be legal for any reasonable language-level memory model.

In the context of a safe language like Java, compiler optimizations can have profound implications for security. Consider Figure 2.11, also from [35]. This example is similar to Figure 2.10, except that the values written to x and y are now the values read from y and x, respectively. Now, consider a compiler optimization that transforms Thread 1 as follows:

```

y = 42;

r1 = x;

if (r1 != 42) {

y = r1;

}

```

If Thread 2 is transformed symmetrically, the outcome r1 == 1 and r2 == 42 is allowed. Note that the transformed code is safe in a single-threaded setting, so a compiler could theoretically implement this transformation (although in practice it is very unlikely). The problem here is that the value 42 appeared "out of thin air": 42 is never assigned to x or y in the original program. Practically, the issue is that the compiler added a speculative write whose value was not justified by the original program.

Out of thin air (OoTA) reads are a potential security hole in a safe language like Java. Hypothetically, untrusted code could gain access to thread-local objects or confidential data (e.g., a user's password). Therefore, Manson et al. (the authors of the Java memory model) concluded that such optimizations, no matter how unlikely, must be explicitly disallowed

by the memory model [35]. In contrast, C and C++ are unsafe languages, so they make no guarantees about OoTA reads [11].

### 2.3 Programming-Language Memory Models

This section discusses the design of memory-consistency models for programming languages in the context of two important examples: the Java memory model [35] and the C/C++ memory model [11]. These models represent two extremes on the design spectrum for memory models. We will describe the Java and C/C++ models using a hybrid of both models' formalizations [35, 11].

### 2.3.1 Definitions

A running program emits a series of actions. The kinds of possible actions vary depending on the synchronization mechanisms provided by the language. For the moment, we will assume that the language supports shared mutable variables x and non-reentrant mutual-exclusion locks l. For brevity, we omit synchronization mechanisms other than locks; we address volatile variables briefly in Section 2.3.2.

Let A be a set of actions, where each action is a triple of a thread ID t, a kind of action k, and a UID (unique ID) u: (t, k, u). Kinds of actions include reads and writes to shared variables and acquires and releases of non-reentrant locks:

Kinds

$$k ::= read(x) \mid write(x) \mid mtx\_lock(l) \mid mtx\_unlock(l)$$

We specify the memory model for a language by giving a set of constraints, or axioms, over executions. Some models are concise and easy to state (e.g., sequential consistency) while models like the JMM are considerably more complex. This axiomatic approach is not the only way to specify a memory model, but it is the most prevalent in the literature, both because the initial formulations of memory models for hardware took this approach [2] and because it is versatile enough to describe a large variety of models.

<sup>&</sup>lt;sup>2</sup>Non-reentrant locks cannot be reacquired by the thread holding the lock.

We describe several axioms shared by all the memory models we will discuss. These axioms rely on several auxiliary structures, which we shall summarize after defining the axioms.

- 1. Let the writes-seen function W be a map from UIDs of read actions in A to UIDs of write actions in A, and let the values-written function V be a map from UIDs for write actions in A to values. These two functions must be defined properly: W is defined on UID u if and only if there exists (t, k, u) ∈ A and k is a read, and V is defined on UID u if and only if there exists (t, k, u) ∈ A and k is a write. Moreover, for all (t, k, u) ∈ A where k is a read and (t', k', W(u)) ∈ A, k and k' must access the same variable and k' must be a write. (This formulation is used by the Java Memory Model; in the C++ model, all read and write actions include the value read or written.)

- 2. The synchronization operations in A must obey mutual exclusion. Assume there is a strict total order  $<_{so}$  over UIDs for synchronization operations (that is, acquire and release operations) in A. Then mutual exclusion imposes the following constraints: acquires and releases of each lock must alternate in the total order  $<_{so}$ ; the first action for each lock in  $<_{so}$  must be an acquire; and the thread that releases a lock must also have been the most recent thread (according to  $<_{so}$ ) to have acquired that lock.

- 3. The execution must satisfy intra-thread consistency. Let the program order  $\leq_{po}$  be a partial order over UIDs such that  $u_1 \leq_{po} u_2$  only if  $u_1$  and  $u_2$  correspond to the same thread ID. Note that the actions of a single thread need not be totally ordered by  $\leq_{po}$ ; for example, C and C++ leave undefined the order of evaluation of function arguments [11]. Then the program (we assume there is some program P associated with A) must be able to produce the actions in A in the order given by  $\leq_{po}$ , according to the sequential (i.e., "intra-thread") semantics of the language. The sequential semantics uses the functions W and V to get a value for each read operation: the value returned by a read u is V(W(u)). Similarly, for every write action u, the value written by the sequential semantics must match the value given by V(u).

4. The program order and synchronization order must be consistent. That is, the reflexive transitive closure of the union of  $\leq_{po}$  and  $<_{so}$  is antisymmetric.

The Java and C/C++ models include other axioms (e.g., for variable initialization), but these four axioms are the most broadly relevant. Gathering the various definitions together, we say that an execution E consists of a program P, a set of actions A, a program order  $\leq_{po}$ , a synchronization order  $<_{so}$ , a writes-seen function W, and a values-written function V:  $E = (P, A, \leq_{po}, <_{so}, W, V)$ . Furthermore, executions satisfying the four constraints listed above are well-formed.

The intra-thread consistency requirement is interesting in that it is unique to language-level memory models. This requirement is the only link between the sequential and concurrent features of the language, so it is crucial in determining the possible legal executions of a program. Hardware memory models may include constructs for data or control dependencies, but they generally ignore details like values being read and written or the semantics of non-memory instructions (e.g., [3]). (An exception is the x86-CC model [41], which includes an instruction semantics as well as an axiomatic model.) We omit the syntax and sequential semantics of the program P; for our purposes, the program is effectively a predicate over executions. (This observation is due to Aspinall and Ševčík [5], who proved the DRF guarantee for the JMM without having to define a sequential semantics.) However, defining the program syntax and semantics is crucial when reasoning about the correctness of compiler optimizations [8, 46].

We will use the notion of a well-formed execution to describe sequential consistency, the Java memory model, and the C++ memory model. For the purposes of exposition, we discuss the C++ model before the Java model, which is considerably more complex. The Java model actually predates the C++ model. The Java section is not necessary for understanding the remainder of this dissertation.

## 2.3.2 Volatile Variables

We can add volatile variables to our semantics by augmenting the syntax of actions:

Kinds

$$k ::= ::= \dots \mid \mathsf{readv}(t, v) \mid \mathsf{writev}(t, v)$$

Volatile reads and writes are included in the synchronization order, and we extend the definition of well-formedness to require that volatile reads and writes exhibit sequentially-consistent semantics. The happens-before order (defined in Section 2.3.4) is extended to include edges from writes to reads of volatile variables.

Volatiles differ from normal variables in that they define ordering constraints. In particular, the compiler cannot optimize away volatile operations using, for instance, redundant read elimination, because removing a volatile operation also changes the happens-before relation of an execution [35].

### 2.3.3 Sequential Consistency

Sequential consistency is our most basic memory model, defining the most intuitive semantics possible for a multithreaded program. In short, the actions of each thread are interleaved in a global order. This global order must be consistent with the program and synchronization orders, and each read must see the most recent write in the global order. Formally, we say a well-formed execution  $E = (P, A, \leq_{po}, <_{so}, W, V)$  is sequentially consistent if there exists a total order  $\leq$  over the UIDs in A such that:

- 1.  $u_1 \leq_{po} u_2$  implies that  $u_1 \leq u_2$ ;

- 2.  $u_1 <_{so} u_2$  implies that  $u_1 < u_2$ ;

- 3. For all reads  $u_r \in A$ , there does not exist a write  $u_w \in A$  such that  $u_w$  and  $u_r$  access the same variable and  $W(u_r) < u_w < u_r$ .

This axiomatic specification of sequential consistency is somewhat oblique, but the intuition is for the actions of all threads to interleave in the natural way.

## 2.3.4 Data Races

Most memory models provide the data-race-free guarantee: programs that are "correctly synchronized" will have simple semantics (i.e., sequential consistency). We have already defined sequential consistency; now we must define the notion of a *correctly synchronized* program. In short, a correctly synchronized program is a program that has no data races.

As discussed in Section 2.1.3, a data race occurs when two threads access the same

location concurrently, and at least one of those accesses is a write. It is difficult to reason about the semantics of a program in the presence of data races, even if the language supports a strong memory model such as sequential consistency. Therefore, most memory models consider a program with data races to be fundamentally erroneous. Following Boehm and Adve [11], we distinguish between two competing definitions of data race, one of which formalizes the intuitive definition given earlier and one of which departs from that intuition. For many languages, these two definitions are equivalent.

A type 1 data race is defined in terms of actions that could have happened at the same time in a sequentially consistent execution. Let  $E = (P, A, \leq_{po}, <_{so}, W, V)$  be a sequentially consistent execution with total order  $\leq$ . Then E contains a type 1 data race if there exist two read/write actions  $(t_1, k_1, u_1)$  and  $(t_2, k_2, u_2) \in A$  such that  $t_1 \neq t_2$ ,  $k_1$  and  $k_2$  access the same location, at least one of  $k_1$  and  $k_2$  is a write, and  $u_1$  and  $u_2$  are consecutive in the sequential order.

A type 2 data race is defined in terms of a partial order on a program execution called the happens-before order. Following the Java memory model [35], we can define the happens-before order as follows (the C++ definition is similar). Two UIDs  $u_1$  and  $u_2$  in a well-formed execution  $(P, A, \leq_{po}, <_{so}, W, V)$  are ordered by the synchronizes-with order  $<_{sw}$  if  $u_1 <_{so} u_2$  and there exists a lock l such that  $u_1$ 's corresponding action is  $mtx\_unlock(l)$  and  $u_2$ 's corresponding action is  $mtx\_lock(l)$ . The happens-before order  $\leq_{hb}$  is then defined as the reflexive transitive closure of the union of  $\leq_{po}$  and  $<_{sw}$ . Finally, two read/write actions  $u_1$  and  $u_2$  form a type 2 data race if  $u_1$  and  $u_2$  are performed by different threads, the actions corresponding to  $u_1$  and  $u_2$  access the same location, at least one of  $u_1$  and  $u_2$  is a write, and  $u_1$  and  $u_2$  are not ordered by happens-before; that is, neither  $u_1 \leq_{hb} u_2$  nor  $u_2 \leq_{hb} u_1$ .

Note that type 2 data races are more general than type 1 data races. If an execution has a type 1 data race, the two actions in question are clearly not ordered by happens-before, and therefore also form a type 2 data race. However, an execution may have a type 2 data race but no type 1 data race (if the racy actions do not happen to occur consecutively in the total order).

For many languages, the distinction between type 1 and type 2 data races is moot, because they can be proved equivalent (a proof for C/C++ is given in Theorem 8.2 of

the PLDI paper introducing the C++11 model [11]). Proving this equivalence consists of finding an execution of the program P in which the actions forming the type 2 data race are consecutive. As we shall see in Section 2.3.5, some types of synchronization invalidate this equivalence. In such instances, the memory model is defined in terms of type 2 data races, making the language less usable to the programmer.

We highlight the difference between type 1 and type 2 data races because they illustrate a design choice where the programmer and the compiler have different demands. Programmers can more easily reason about type 1 data races, because the idea of two actions occurring simultaneously is simple and intuitive. Compiler designers require the precision of the happens-before relation to reason carefully about code transformations. Therefore it is ideal for languages to support type 1/type 2 data race equivalence if possible.

#### 2.3.5 The C++ Memory Model

Given the definition of a type 1 data race, the C/C++ memory model is simple [11]:

- 1. If a program is type 1 data-race-free, then all executions of that program are sequentially consistent.

- 2. If a program is not type 1 data-race-free, then the program's semantics is undefined.

In effect, the model declares that "there are no benign data races" in C and C++

[11]. A program that includes a data race could (figuratively) set the computer on fire.

Drawbacks of this approach include that debugging racy programs is difficult, and of course that we have none of the safety or security guarantees provided by Java's model. Boehm and Adve, in their overview of the model [11], argue that data races are too difficult to deal with in an unsafe language like C++, and give an example in which a data race effectively causes the program to start executing code at an arbitrary address. Leaving the semantics of incorrectly synchronized programs undefined significantly simplifies the work of the compiler. For example, eliminating a redundant read is safe as long as there are no synchronization operations between the two reads, because no other thread could possibly update the value of the location without causing a data race. (This insight will be crucial to our work on compiler optimization in Chapter 4.)

#### Complications

As observed by Boehm [8], adding a mtx\_trylock primitive (which attempts to acquire a lock and succeeds if and only if the lock is available) to the set of synchronization primitives available to the language impacts the semantics of the memory model. To be precise, the use of mtx\_trylock invalidates the equivalence of type 1 and type 2 data races, unless we strengthen the happens-before relation to include edges between acquire and trylock operations. However, this change would disallow a key compiler optimization, namely moving memory actions into critical sections by reordering them with lock acquires (i.e., roach-motel reordering [35]). The C/C++ model instead redefines the semantics of mtx\_trylock such that it can spuriously fail to acquire the lock even if the lock is available, neatly sidestepping this semantic issue [11].

The C/C++ model is further complicated by the assumption that there is a total order over all synchronization operations in an execution ( $<_{so}$  in our formalism). Some architectures do not support this requirement, which makes it impossible to reason about the semantics of a program with respect to a sequentially consistent execution. Instead, the C/C++ memory model provides an "expert" version in which synchronization operations (or, in their terminology, "low-level atomics") do not have a total global order. This model is considerably more complicated than the model without low-level atomics, but allows for finely-tuned optimization of low-level concurrent code [11, 22, 23].

Despite these complications, the C/C++ model is, for the vast majority of programmers, very simple. Most programmers must simply avoid type 1 data races, and the compiler will guarantee sequentially consistent semantics. This model represents an interesting point in the design space of memory models, where we sacrifice security and safety in favor of simplicity and flexibility.

#### 2.3.6 The Java Memory Model

This section discusses the Java memory model. Although the information presented provides useful background, it is not essential since the rest of the dissertation focuses on C and C++.

The Java memory model (JMM), developed by Manson, Pugh, and Adve with the input

of the Java community [35], differs from the C/C++ model in that the Java model defines the semantics of all programs, even those with races. This requirement comes from Java's status as a type-safe language with strong security guarantees. The JMM is the state of the art for defining a precise and secure memory model for a type-safe language.

The JMM is a data-race-free model, guaranteeing sequentially consistent semantics for correctly synchronized programs. (Unlike C and C++, the JMM defines data races using the type 2 definition; type 1 and type 2 data races are not equivalent in Java [9].) The main hurdle in formulating the JMM was to define safe but efficient semantics for incorrectly synchronized code.

#### Out of Thin Air Reads

In order to maintain Java's security guarantees, the memory model goes to great lengths to disallow so-called *out of thin air* (OoTA) reads. OoTA reads (as in Figure 2.11) return values that do not occur in any reasonable interpretation of the program semantics, even when allowing for standard compiler transformations. If values were permitted to appear out of thin air, it could theoretically result in threads getting access to confidential data by exploiting incorrectly synchronized programs. Although real compilers are unlikely to compile programs such that values appear out of thin air, it is critical that the memory model explicitly disallow such behavior.

An intuitive but imprecise definition of Java's OoTA restriction is as follows: a thread must never see a value for a read that could never be written to that location in a sequentially consistent execution. However, the JMM's definition of OoTA is somewhat more restrictive: it states that "early execution of an action does not result in an undesirable causal cycle if its occurrence is not dependent on a read returning a value from a data race" [35]. This definition is confusing, but the intuition is that that speculative executions (which are used to justify early writes) should not rely on one possible outcome of a data race if the final execution relies on a different outcome.

# Overview of the JMM

The JMM disallows causal cycles by requiring that every execution be justified by a series of intermediate executions. Formally, in order to justify a well-formed execution E, we must build up a series of executions  $E_0 \dots E_n$  where  $E = E_n$  and each execution has the same program P.<sup>3</sup> Execution  $E_i$  "commits" a set of actions  $C_i \subseteq A_i$ , such that  $C_0 = \{\}$ ,  $C_0 \subset C_1 \subset \dots \subset C_n$  and  $C_n = A$ . In other words, each successive execution in the series justifies one or more of the actions in the final execution, cumulatively justifying the entire execution.

Given this notion of a set of justifying executions, we can characterize the JMM as follows: the JMM is a set of axioms which, when taken together, describe all legal series of justifying executions. A (very) simplified explanation of the axioms is that each justifying execution must be both well-formed (as defined in Section 2.3.1) and well-behaved, which means that all reads see writes that happen-before them. However, committed reads do not need to be well-behaved, which allows executions to have read-write data races. The JMM, then, defines a commit procedure wherein we iteratively commit non-well-behaved reads, fixing the write seen by the committed read in order to disallow causal cycles. (We must also commit all other actions in the execution, including writes, synchronization operations and well-behaved reads, but the trick is in committing non-well-behaved reads.)