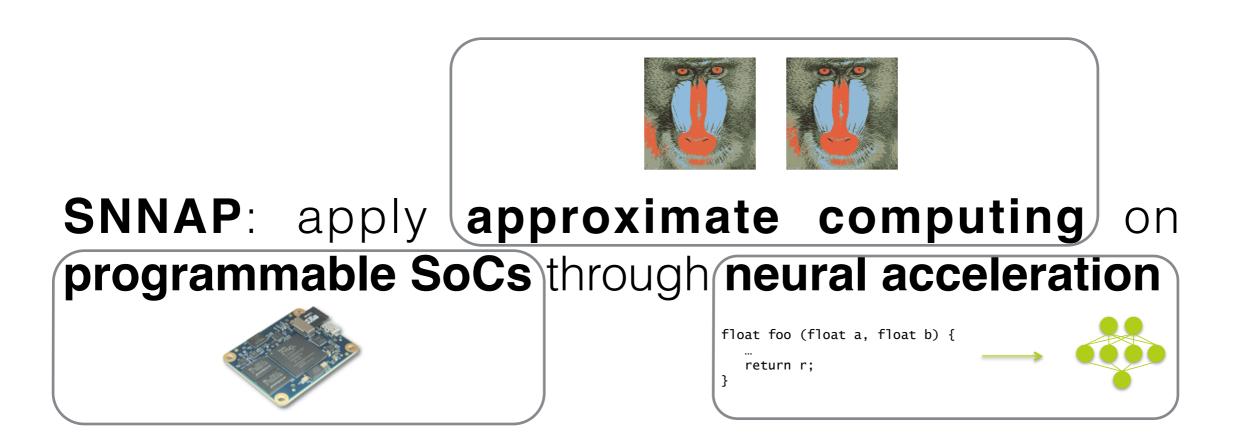

# SNNAP: Approximate Computing on Programmable SoCs via Neural Acceleration

Thierry Moreau

Mark Wyse

Jacob Nelson

Adrian Sampson

Hadi Esmaeilzadeh Luis Ceze Mark Oskin

# Approximate Computing

Expose quality-performance trade-offs

# Approximate Computing

Expose quality-performance trade-offs

**X** Expensive

X Approximate

# Approximate Computing

Expose quality-performance trade-offs

Approximate

Domains include image processing, machine learning, search, physical simulation, multimedia etc.

### Neural Acceleration

```

float foo (float a, float b)

{

...

return val;

approximation

float foo (float a, float b)

acceleration

```

### Neural Acceleration

```

float foo (float a, float b)

{

...

return val;

approximation

float foo (float a, float b)

acceleration

```

Esmaeilzadeh et al. [MICRO 2012]

SNNAP

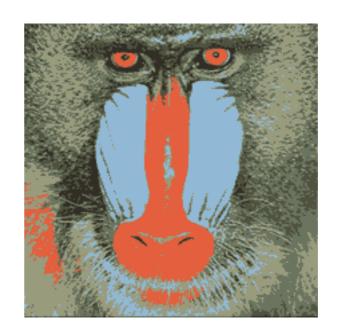

### SNNAP

```

float foo (float a, float b)

{

...

return val;

approximation

float foo (float a, float b)

acceleration

```

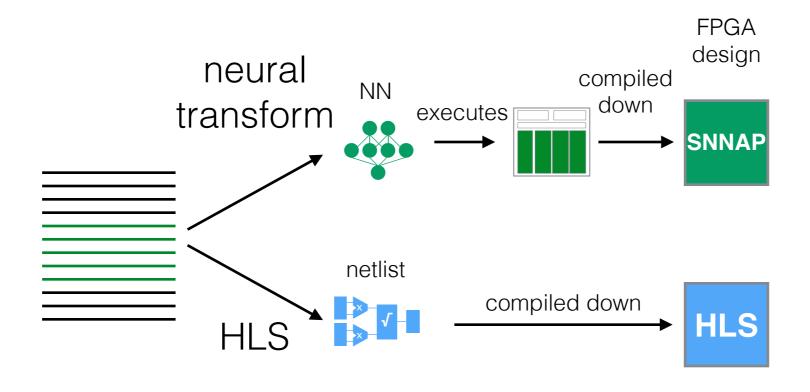

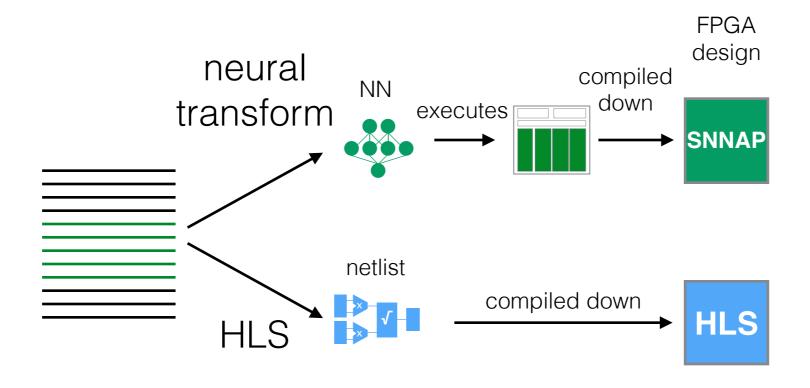

A neural processing unit on off-the-shelf Programmable SoCs

3.8x speedup and 2.8x efficiency gains

offers an alternative to HLS tools for neural acceleration

### Talk Outline

Introduction

#### **Programming model**

SNNAP design:

- Efficient neural network evaluation

- Low-latency communication

Evaluation & Comparison with HLS

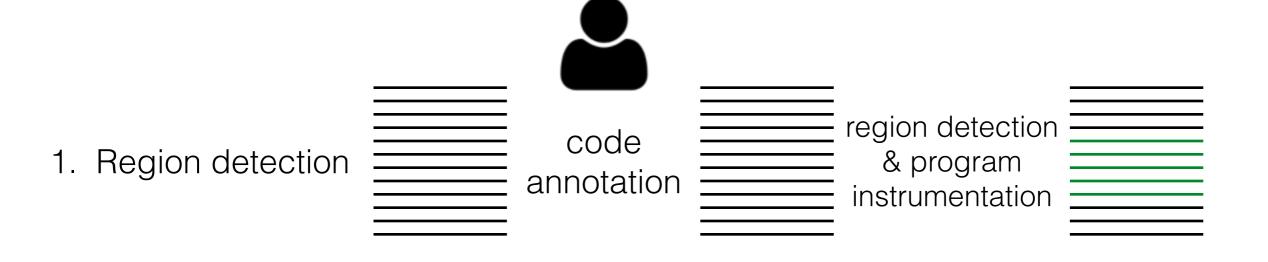

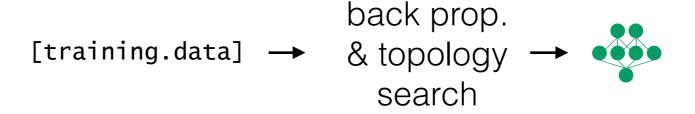

### Background: Compilation

2. ANN Training

3. Code Generation

# Programming Model

sobel

```

float sobel (float* p);

Image src;

Image dst;

while (true) {

src = read_from_camera();

for (y=0; y < h; ++y) {

for (x=0; x < w; ++x) {

dst.p[y][x] = sobel(& src.p[y][x]);

display(dst);

```

# Programming Model

```

sobel

```

```

APPROX float sobel (APPROX float* p);

APPROX Image src;

APPROX Image dst;

no side effects

while (true) {

src = read_from_camera();

executes often

for (y=0; y < h; ++y) {

for (x=0; x < w; ++x) {

dst.p[y][x] = sobel(& src.p[y][x]);

display(dst);

```

ACCEPT: compilation framework for approximate programs

#### Talk Outline

Introduction

Programming model

SNNAP design:

- Efficient neural network evaluation

- Low-latency communication

Evaluation & Comparison with HLS

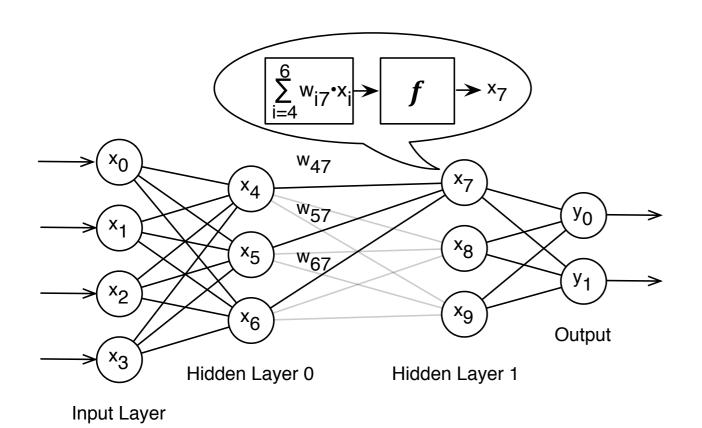

### Background: Multi-Layer Perceptrons

#### neural network

computing a single layer

$$\begin{bmatrix} x_7 \\ x_8 \\ x_9 \end{bmatrix} = f \begin{pmatrix} \begin{bmatrix} w_{67} & w_{57} & w_{47} \\ w_{68} & w_{58} & w_{48} \\ w_{69} & w_{59} & w_{49} \end{bmatrix} \begin{bmatrix} x_6 \\ x_5 \\ x_4 \end{bmatrix}$$

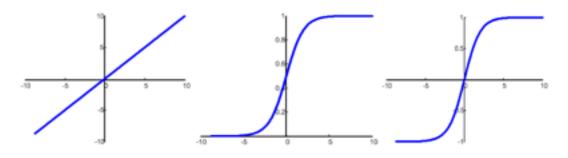

activation function f

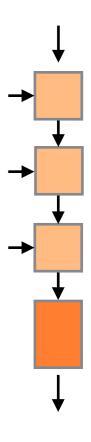

### Background: Systolic Arrays

computing a single layer

$$\begin{bmatrix} X_7 \\ X_8 \\ X_9 \end{bmatrix} = f \begin{pmatrix} W_{67} & W_{57} & W_{47} \\ W_{68} & W_{58} & W_{48} \\ W_{69} & W_{59} & W_{49} \end{pmatrix} \begin{bmatrix} X_6 \\ X_5 \\ X_4 \end{bmatrix}$$

systolic array

### Background: Systolic Arrays

systolic array

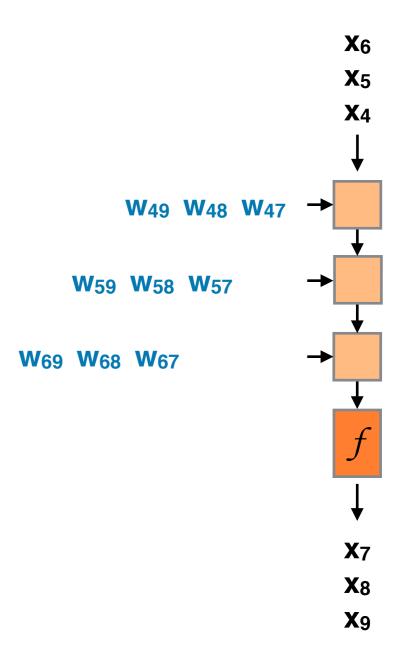

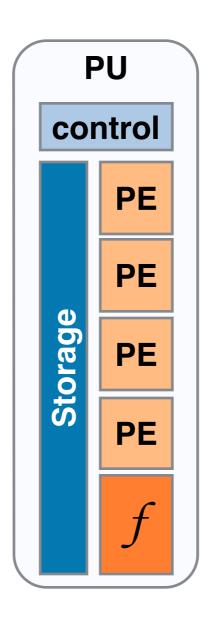

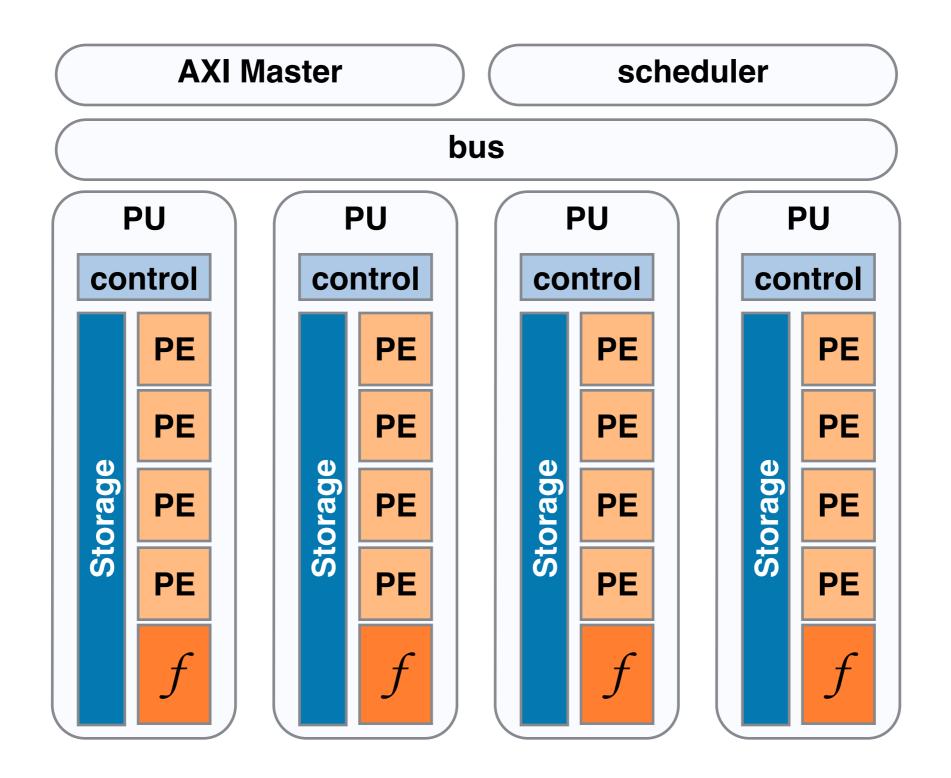

#### PU Micro-Architecture

systolic array

**X**6 **X**5 **X**4 W49 W48 W47 W59 W58 W57 W69 W68 W67 **X**7 Xa **X**9

processing unit

1 - processing elements in DSP logic

- 2 local storage for synaptic weights

- 3 sigmoid unit implements nonlinear activation functions

4 - vertically micro-coded sequencer

# Multi-Processing Units

#### Talk Outline

Introduction

Programming model

#### SNNAP design:

- Efficient neural network evaluation

- Low-latency communication

Evaluation & Comparison with HLS

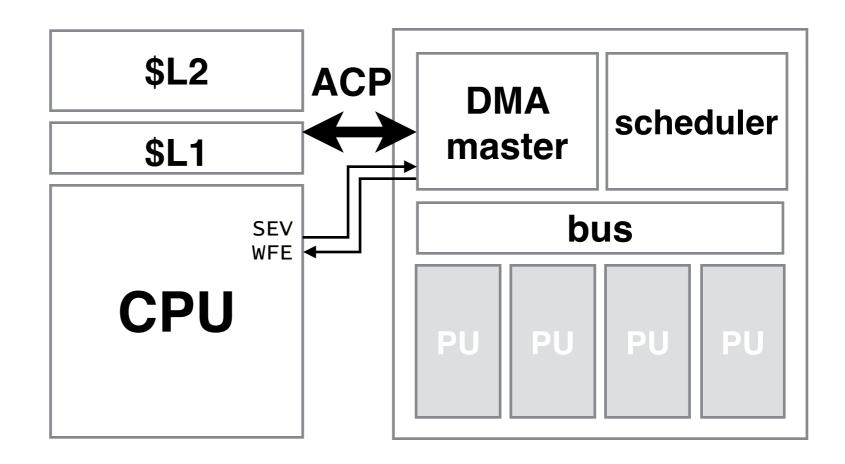

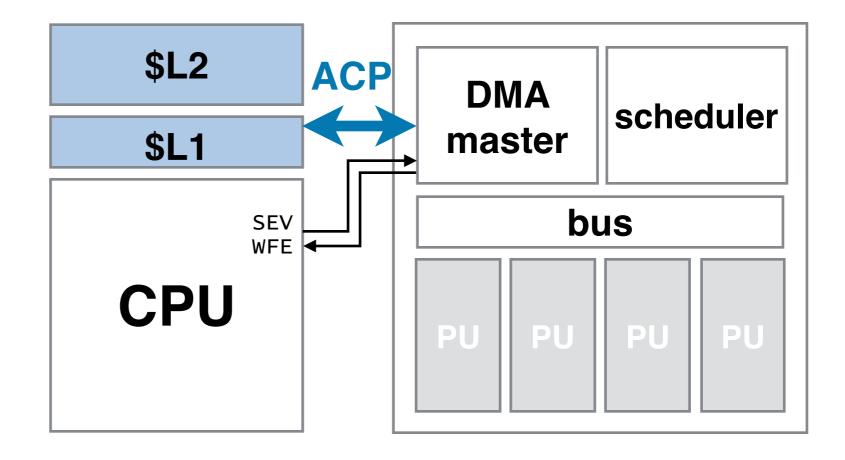

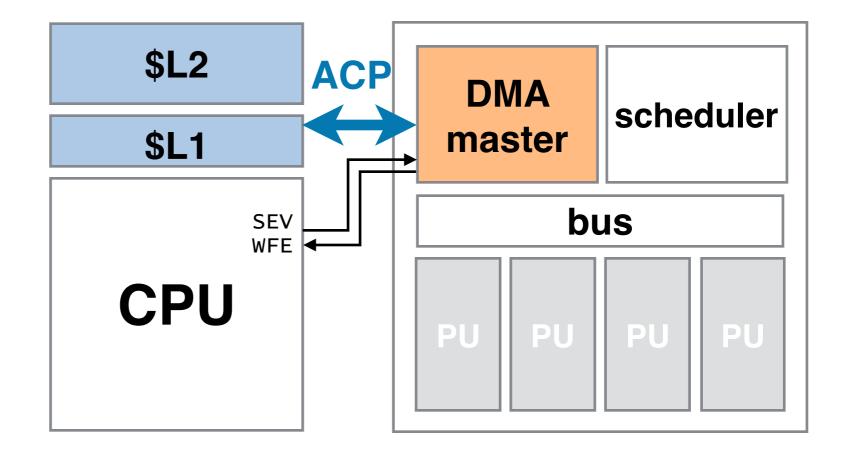

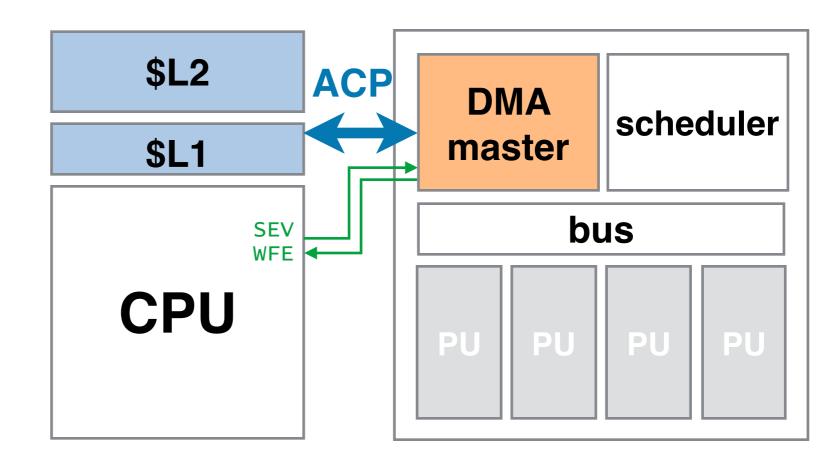

#### Interface requirements:

- Low-latency data transfer

- Fast signaling

#### Interface requirements:

- Low-latency data transfer

- Fast signaling

coherent reads & writes with accelerator coherency port

#### Interface requirements:

- Low-latency data transfer

- Fast signaling

coherent reads & writes with accelerator coherency port

custom mastering interface

#### Interface requirements:

- Low-latency data transfer

- Fast signaling

coherent reads & writes with accelerator coherency port

custom mastering interface

low-latency event signaling, sleep & wakeup

#### Talk Outline

Introduction

Programming model

SNNAP design:

- Efficient neural network evaluation

- Low-latency communication

**Evaluation & Comparison with HLS**

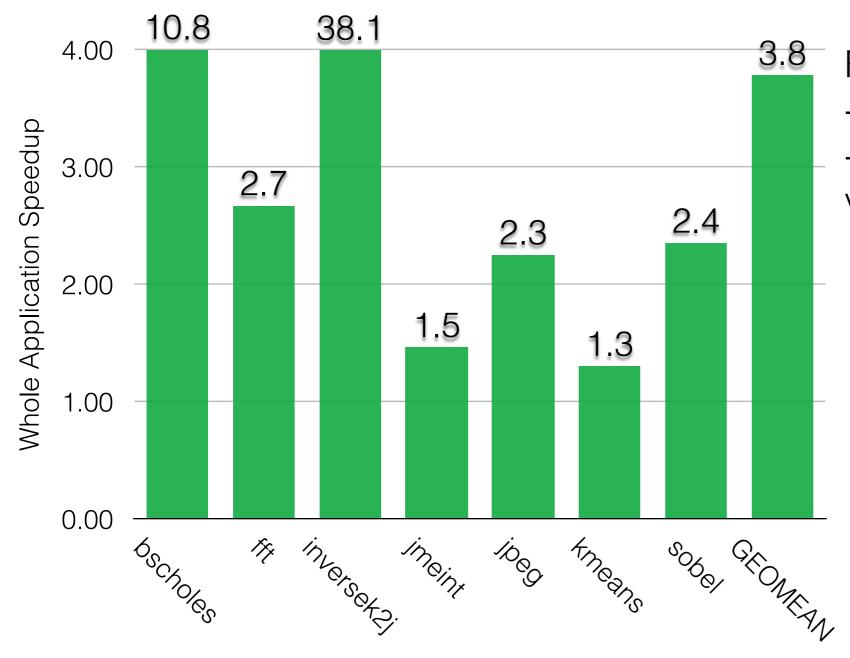

#### Evaluation

Neural acceleration on SNNAP (8x8 configuration, clocked at 1/4 of f<sub>CPU</sub>) vs. precise CPU execution

#### Evaluation

Neural acceleration on SNNAP (8x8 configuration, clocked at 1/4 of f<sub>CPU</sub>) vs. precise CPU execution

| application  | domain         | error metric |

|--------------|----------------|--------------|

| blackscholes | option pricing | MSE          |

| fft          | DSP            | MSE          |

| inversek2j   | robotics       | MSE          |

| jmeint       | 3D-modeling    | miss rate    |

| jpeg         | compression    | image diff   |

| kmeans       | ML             | image diff   |

| sobel        | vision         | image diff   |

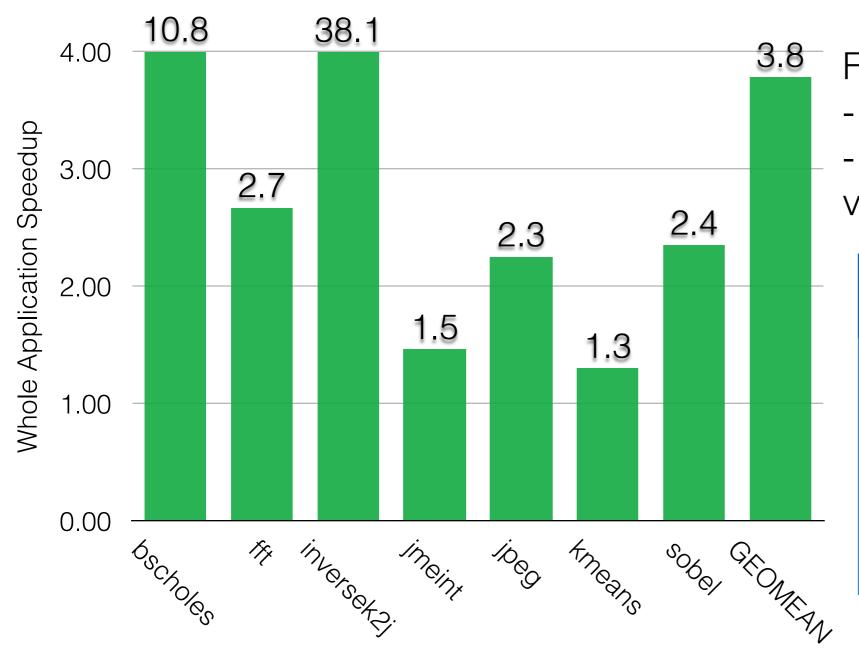

# Speedup

#### Factors:

- Amdahl's Speedup

- Cost of instructions on CPU vs. cost of NN on SNNAP

# Speedup

#### Factors:

- Amdahl's Speedup

- Cost of instructions on CPU vs. cost of NN on SNNAP

|                     | inversek2j     | kmeans    |

|---------------------|----------------|-----------|

| Amdahl's<br>Speedup | >100x          | 1.47x     |

| CPU cost            | 1660<br>cycles | 29 cycles |

| NN hidden<br>layers | 1              | 2         |

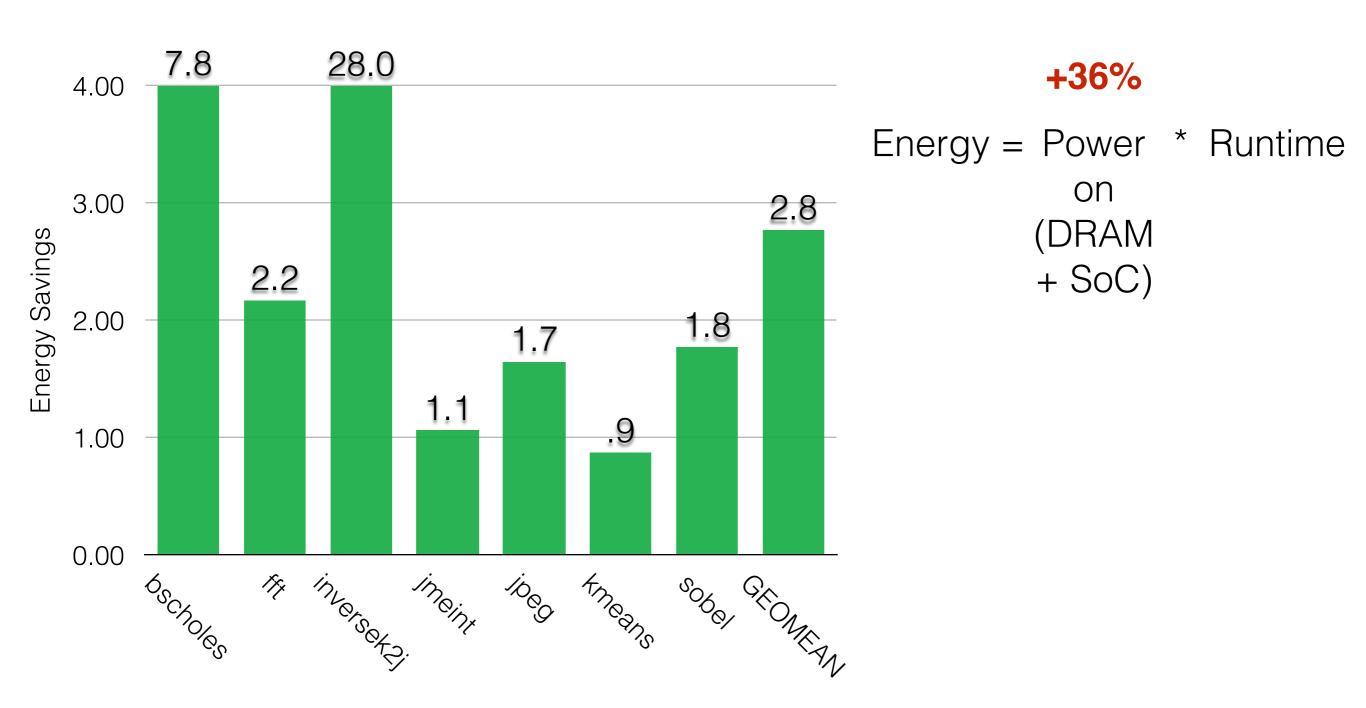

# Energy Savings

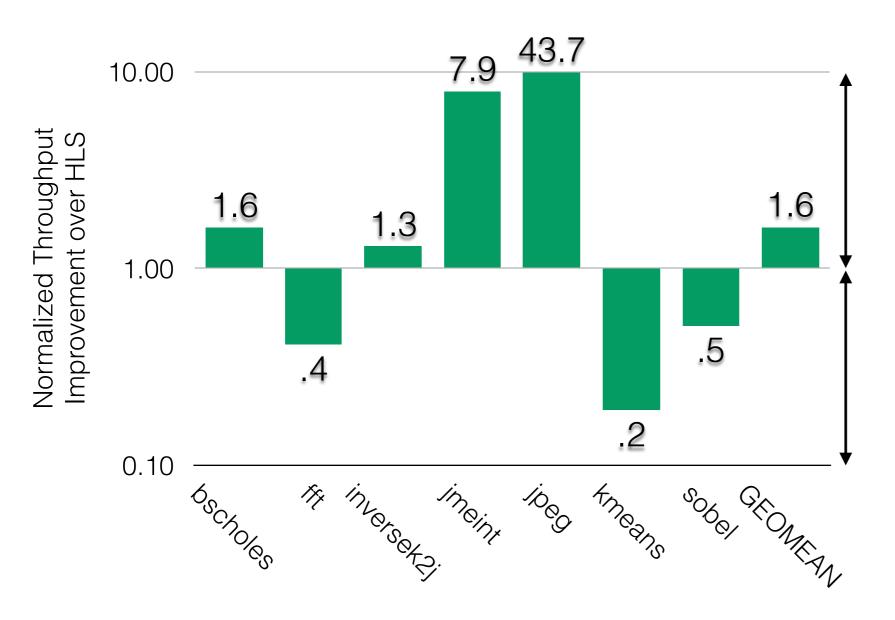

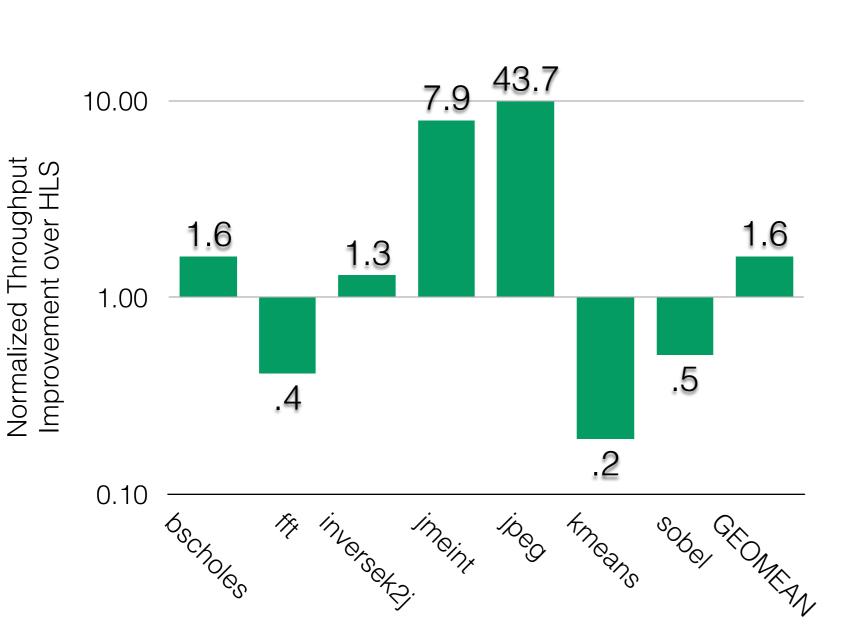

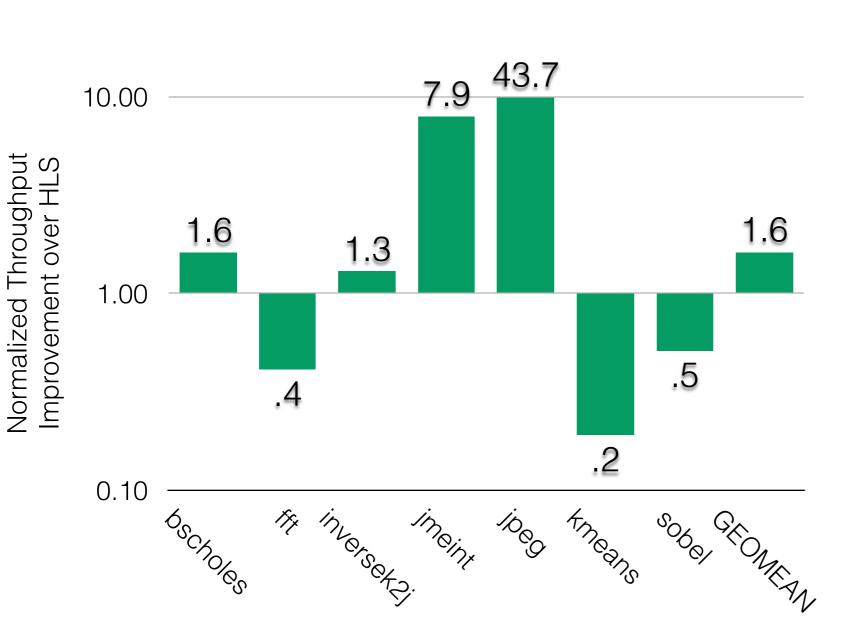

#### HW Acceleration

Neural Acceleration with SNNAP vs.

High Level Synthesis Compilers

which one should you use?

#### Resource-normalized throughput:

- pipeline invocation interval

- maximum frequency

- resource utilization

Neural Acceleration is better

HLS is better

|                 | Neural<br>Accel. | HLS |

|-----------------|------------------|-----|

| Precision       |                  |     |

| Virtualization  |                  |     |

| Performance     |                  |     |

| Programmability |                  |     |

|                 | Neural<br>Accel. | HLS |

|-----------------|------------------|-----|

| Precision       |                  |     |

| Virtualization  |                  |     |

| Performance     | ~                | ~   |

| Programmability |                  |     |

### Conclusion

3.8x speedup & 2.8x energy savings neural acceleration is a viable alternative to HLS

#### SNNAP:

# Approximate Computing on Programmable SoCs via Neural Acceleration

Thierry Moreau: moreau@uw.edu

Mark Wyse Jacob Nelson Adrian Sampson Hadi Esmaeilzadeh Luis Ceze Mark Oskin

http://sampa.cs.washington.edu/